# ECSE 487 COMPUTER ARCHITECTURE LAB

# ASSIGNMENT 1: MULTI MODE BARREL SHIFTER

By: Simon Foucher 260 223 197 Simon.foucher@mail.mcgill.ca

Monday, Jan 26<sup>th</sup> 2009

## 2.0 Lab description

Design a multi-mode barrel shifter. The unit has 3 inputs: IN, N and S, and has a single output: OUT. The shifter accepts an array of 8 bits in parallel through IN and shifts it by any number of bits between 0 and 7, encoded in binary in the input N. The shifted vector is outputted in OUT.

The shifter has 4 modes of operation, encoded by the 3<sup>rd</sup> input S as follows:

- "00": Rotate shift right

- "01": Shift Logical Left

- "10": Shift Logical Right

- "11": Shift Arithmetic Right

The design has to be done in 3 different approaches:

- Behavioral: the VHDL describes the behavior of the data manipulation

- Structural: the design is separated between data buses which carry the data from the input to the output, and control lines which select how the data is manipulated along its path. In this type of design, every connection is explicitly described at the gate level.

- Pipelined: The structural design is split up into data flow stages, and registers are placed between each stage. Like an assembly line, the pipelined shifter can work on multiple operations at once. This design is optimized for maximum clock speed, since once loaded, it will produce one operation per clock pulse.

# 3.1. Behavioral Shifter

# I) Description of the methodology followed.

[file: /VHDL/Q1\_BEHAVIORAL.vhd]

This design was made using a single process and 2 case statements. The first case statement reads the S input and detects the mode of operation. From there, the second case statement reads the value in the N input. Based on those 2 cases, we use a simple concatenation statement to produce the shift.

When in barrel shift mode, we concatenate the input with itself. When in logical shift, we concatenate the input with the required amount of 0 and when in arithmetic shift, we concatenate the input with one or many times it's most significant bit.

#### **II) Documented VHDL source code for all entities.**

#### /VHDL/Q1\_BEHAVIORAL.vhd

#### III) Simulation results (traces) to show that your design operates correctly.

Using the macro found here, we tested a few critical cases to assess the quality of the shifter.

#### /MACRO/MACRO\_BEHAV.TXT And here is the simulated result:

| /n            | 010    | 010             |                 |                  |           |                  |           |             |          |

|---------------|--------|-----------------|-----------------|------------------|-----------|------------------|-----------|-------------|----------|

| 10            | 11     | 00              | 101             | (10              | 111       | 200              | .01       | 10          | Y11      |

| с 8<br>Колтон | 011100 |                 | .01             | <u> </u>         | 1         | 1                | .01       | <u>, 10</u> | <u> </u> |

| /input        |        | 11110010        |                 |                  |           | 01110010         |           |             |          |

| /output       | 000111 | <u>10111100</u> | <u>11001000</u> | <u>,00111100</u> | (11111100 | <u>,10011100</u> | (11001000 | 00011100    |          |

FIGURE 3.1.1: Wave pattern when running /MACRO/MACRO\_BEHAV.TXT

We performed a shift by 2 bits in all 4 modes of operation with the most significant bit set to 0 (first series of 4 tests) then set to 1 (second set of 4). This was only to tweak any functional errors. A more exhaustive test was performed with the testbench.

# **IV)** Testbench

/VHDL/TESTBENCH\_BEHAVIORAL.vhd

Notes:

- Ensure to include VHDL '93 Language Syntax before compiling for shift operators libraries

- Best viewed with 4 spaces tab indents (for aligned code)

- With the selected clock speed, 0.33mS of simulation is sufficient to run through all the cases (run 0.33ms)

- A more efficient version of this testbench was developed for the pipelined shifter (see 3.3.IV)

The testbench operated using a finite state machine with 5 state named with what function they perform and the S code associated with this function (ex: SLL\_10 = Shift Logical Left, S <= "10"). After a reset, the process starts in mode ROR\_00 with every bits of the test signals N\_s and INPUT\_s set to 0.

INPUT\_s is 9 bits long (one more than the required input for the DUT). The 8 least significant bits are fed as an input to the DUT and then INPUT\_s in incremented by 1 at every clock pulse. The most significant bit is used as a flag to notify when all the possible cases have been tested. In other words, if we start by "000000000" and increment by 1 at every iterations, once we reach "100000000", every single 8 bit combinations have been exposed to the DUT by the 8 LSBs of the vector. This condition is detected by the statement "while INPUT\_s < 256".

The same strategy is used for the N\_s vector, 4 bits long, of which the 3 LSBs are fed as an N input to the DUT. N\_s is initialized at "0000" and every time we exhaust a list of 256 INPUT\_s vectors, N\_s is incremented by one. Once we reach N = "1000" or N = 8, we have exhausted every required values of N (0 to 7) for the DUT and the Finite State Machine transitions to the next state.

At any moment of the testing, the 8 LSBs of INPUT\_s are manually shifted by N\_s places by the VHDL Code, and the result is compared to the output of the DUT. If a divergence is detected, ERR is set to 1 to notify of the error mode.

After all 4 states have been fully tested, the FSM enters its "finished" state and ERR is set to 1 (the signal is recycled as a 'done' signal; combined with the FSM's 'finished' state).

| al/n_s      | 0000     | 011 | 1      |                     |    | 1000     |   | 0000     |  |  |

|-------------|----------|-----|--------|---------------------|----|----------|---|----------|--|--|

| al/s_s      | 00       | 11  |        |                     |    |          |   | (00      |  |  |

| al/input_s  | 000000   | 011 | 111111 | <u> 10000000</u>    | io | 00000000 | 0 |          |  |  |

| al/output_s | 000000   | 111 | 11111  | <u> 200000000 (</u> |    |          |   |          |  |  |

| al/clock    | 0        |     |        |                     |    |          |   |          |  |  |

| al/err      | 1        |     |        |                     |    |          |   |          |  |  |

| al/state    | finished | sar | 11     |                     |    |          |   | finished |  |  |

|             |          |     |        |                     |    |          |   |          |  |  |

FIGURE 3.1.2: ERR (in red) is asserted and state is set to 'finished' when the list of all possible inputs ih exhausted.

V) Synthesis for maximum speed and minimum area.

VI) Summary of resources and performance achieved in term of throughput and latency.

# 3.2. Structural Shifter

I)Description of the methodology followed

/SCEMATICS/STRUCTURAL\_DRAWING.pdf : High resolution schematic /VHDL/Q1\_STRUCTURAL.vhd : Main device /VHDL/MUX4.vhd and MUX8.vhd: Components used

The main design strategies used was to develop the structural design in data flow stages, to facilitate the conversion into a pipelined version in question 2. We also tried to create components for repeated code (mostly muxes).

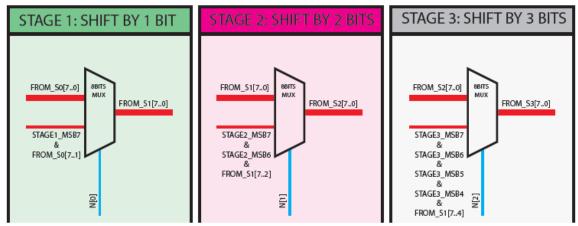

Every stage is composed of an 8 bit wide bus Multiplexes with a single select line, designed separately as a component (MUX8.vhd). The barrel shifter was initially split into 3 stages. Stage one (controlled by the LSB of N) selects between the input ant the input shifted by one place. Stage 2 selects between the input from stage 1 and this input shifted by 2 places, and is controlled by the central bit of N. Stage 3, controlled by the MSB of N selects between the output of stage 2 and this output shifted by 4 places.

By doing so, every combinations of the 3 bits of N can select between any combinations of 1+2+4, or shift anywhere from 0 to 7 inclusively.

It might be more intuitive to do the reverse order of stages (i.e. have the first stage connected to the MSB of N and shift by 4), but the design was based on the following site and works just as good either way:

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/10-gates/60-barrel/shifter8.html

FIGURE 3.2.1: main stages of the structural shifter (red = Data Path, Blue = control lines)

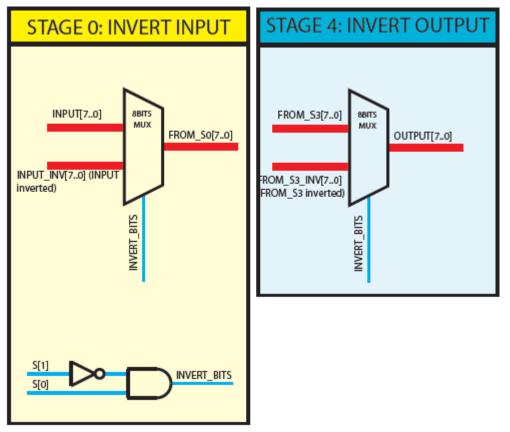

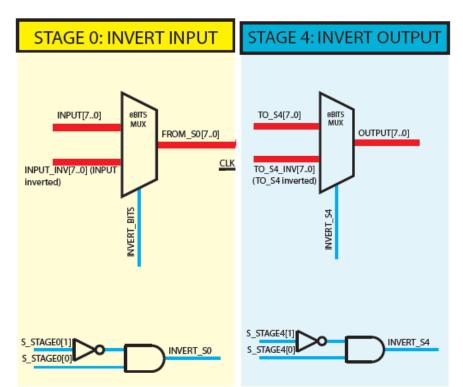

To simplify the logic, the barrel shifter is only capable of shifting right (since this covers  $\frac{3}{4}$  of required operations). In order to accommodate for a SLL, both the input and the outputs can be reversed simultaneously in 2 additional stages (stage 0 and stage 4). The muxes used in those stages are controlled by a signal which gets asserted only when shifting left (INVERT\_BITS <= NOT S(1) AND S(0)).

**FIGURE 3.2.2:** Added stages 0 and 4 to invert the bits when performing a left shift with a right barrel shifter (red = Data Path, Blue = control lines)

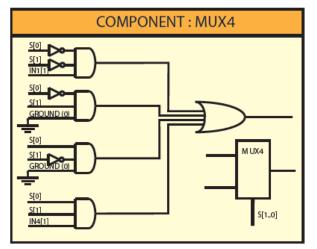

The most significant bit(s) fed to the shifted input passes through a special purpose multiplexer (MUX4.vhd). Using S (mode of operation) as a control line, this mux selects between the LSB(s) of the previous stage when in barrel mode, '0' when on shift Logical Mode, and the MSB of the previous stage when shifting in arithmetic mode.

FIGURE 3.2.3: Special purpose mux to select the MSB feed when shifting

The stage 1 (shifts 1 place) has one of these units, stage 2 (shifts 2 places) has 2 and stage 3 (shifts 4 places) has 4.

II) Documented VHDL source code for all entities. /VHDL/Q1\_STRUCTURAL.vhd : Main device /VHDL/MUX4.vhd: Component used /VHDL/MUX8.vhd: Component used

III) Simulation results (traces) to show that your design operates correctly.

Since the most delicate part of this design was a correct data path between the input and the output, before running the testbench, we used a macro to check the proper functioning of the shifting multiplexers. The main focus was to test every combination of N. In order to do so, individual bits of the N vector were forced into clocks at different frequencies to naturally oscillate in a 3 bit binary count.

/MACROS/MACRO\_STRUCT.TXT (Note: every mode of operation is the macro is meant to be used on SEPARATE simulations)

We can observe the proper amounts of bits being shifted (in yellow), as well as a look at the shifted output of every stages (even is not selected)

| 'input         | 111100 | 11110000 |          |          |          |          |          |          |          |             |

|----------------|--------|----------|----------|----------|----------|----------|----------|----------|----------|-------------|

| 'n             | 110    | 111      | 110      | (101     | (100     | 011      | 010      | 001      | 000      | 111         |

| 's             | 10     | 10       |          |          |          |          |          |          |          |             |

| 'output        | 000000 | 00000001 | 00000011 | 00000111 | 00001111 | 00011110 | 00111100 | 01111000 | 11110000 | 00000001    |

| ′invert_bits   | 0      |          |          |          |          |          |          |          |          |             |

| 'input_inv     | 000011 | 00001111 |          |          |          |          |          |          |          |             |

| from_s3_inv    | 110000 | 10000000 | 11000000 | 11100000 | 11110000 | 01111000 | 00111100 | 00011110 | 00001111 | 10000000    |

| 'from_s0       | 111100 | 11110000 |          |          |          |          |          |          |          |             |

| /from_s1       | 111100 | 01111000 | 11110000 | 01111000 | 11110000 | 01111000 | 11110000 | 01111000 | 11110000 | 01111000    |

| /from_s2       | 001111 | 00011110 | 00111100 | 01111000 | 11110000 | 00011110 | 00111100 | 01111000 | 11110000 | 00011110    |

| /from_s3       | 000000 | 00000001 | 00000011 | 00000111 | 00001111 | 00011110 | 00111100 | 01111000 | 11110000 | 00000001    |

| 'shifted_feed1 | 011110 | 01111000 |          |          |          |          |          |          |          |             |

| /shifted_feed2 | 001111 | 00011110 | 00111100 | 00011110 | 00111100 | 00011110 | 00111100 | 00011110 | 00111100 | 00011110    |

| /shifted_feed3 | 000000 | 00000001 | 00000011 | 00000111 | 00001111 | 00000001 | 00000011 | 00000111 | 00001111 | (00000001 } |

FIGURE 3.2.4: Shifting logical right, result observed in yellow.

## **IV)** Testbench

/VHDL/TESTBENCH\_STRUCTURAL.vhd

The testbench used is identical to the one used for the behavioral tests, with the replacement of the DUT (see 3.1. IV for details)

## V) Synthesis for maximum speed and minimum area.

**VI**) Summary of resources and performance achieved in term of throughput and latency.

# 3.3. Pipelined Shifter

I) Description of the methodology followed (including any figures that help document your design) /SCEMATICS/PIPELINED\_DRAWING.pdf : High resolution schematic /VHDL/Q2\_PIPELINED.vhd : Main device /VHDL/MUX4.vhd and MUX8.vhd: Component Multiplexers used /VHDL/DFF\_8BITS.vhd: a regular 8 bit wide bus DFF /VHDL/DFF\_VAR\_DELAY.vhd: the main timing controller

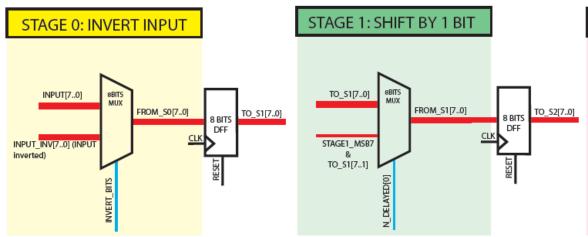

Since the structural design was made with pipelining in mind, only a few upgrades from that model were required to enable pipelining.

The datapath was modified by inserting D flip flop between each stage to capture the data after the last stage has processed it.

Figure 3.3.1: D Flip Flops were added between each Staged of data manipulations. Here we can observe 2 of them after Stage 0 and Stage 1.

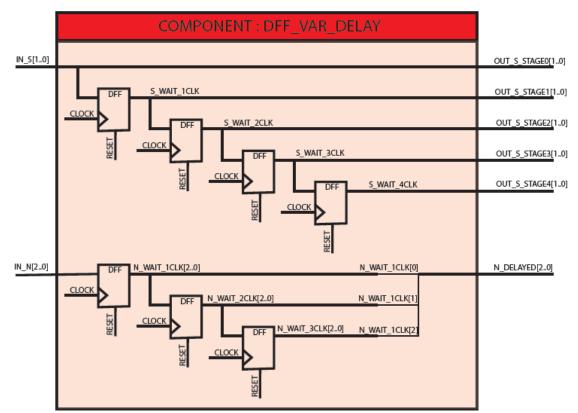

Because of the pipelining, different stages would be executing different instructions simultaneously, so it was necessary to design a timing controller. The controller was encapsulated in a component to facilitate the potential for future upgrades of the shifter. (called: DFF\_VAR\_DELAY.vhd)

The controller inputs N and S and outputs them at different delays. The delays for the S signals match the Stage's names. (Stage 0 takes S\_WAIT\_1CLK, Stage 3 takes S\_WAIT\_3CLK, etc...). There was no absolute necessity to output S\_WAIT\_0CLK, as it is the input directly fed back as an output, but is was implemented in this matter such that only the controller was "allowed" to control the data. (i.e. instead of connecting both S into the controller and into Stage 0, S in only fed to the controller and the controller manages all the Stages). As for N, all 3 bits are delayed by 1, 2 and 3 clock cycle to arrive on time to stages 1, 2 and 3 (Stages 0 and 4 do not need N). Further down the controller, a single bit from each level of delay is selected and recombined in a vector called "N\_DELAYED" which mimics the original N vector which can be reconnected the same way as N was connected in the non Pipelined design. It was not necessary to age all 3 bits by 3 clock cycles (the bare minimum was 1 clock pulse for all 3 lines, 2 clock pulses for the lines going to Stages 2 and 3, and 3 clock pulses only for the bit going to Stage 3). It has been implemented this way for easier understanding and could be changed to reduce the hardware consumption if necessary).

Figure 3.3.2: The controller inputs S and outputs it at different delays for every stages. It also receives N and delays the signals to arrive on time at the muxes.

The input S and S got connected to this controller, and the output of the controller was connected to the control lines of the circuit.

The only other modification made was to add a second AND to stage 4 in order to interpret a reverse signal if needed. To save hardware, we could also have captured the INVERT\_S0 bit and age it 4 clock pulses before sending it to stage 5, but this approach was easier and faster to implement.

Figure 3.3.3: The inverting select hardware was duplicated and the S signal got aged. A better approach would have been to age the invert signal and reuse it in Stage 4. This vould have saved an inverter, an AND gate and the aging flipFlopc could be a single bit wide instead of 2 bits for the S signal.

#### **II) Documented VHDL source code for all entities.**

VHDL/Q2\_PIPELINED.vhd : Main device /VHDL/MUX4.vhd and MUX8.vhd: Component Multiplexers used /VHDL/DFF\_8BITS.vhd: a regular 8 bit wide bus DFF /VHDL/DFF\_VAR\_DELAY.vhd: the main timing controller

#### III) Simulation results (traces) to show that your design operates correctly.

Before running a full testbench, the following macro was used to make sure the timing was accurate.

/MACROS/MACRO\_PIPELINED.txt

The first set of tests performs a left shift, which requires the use of Stage 0, 1 and 4. In the following wave result, we can observe the result trickling down the data pats as required.

|        |                                                          |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     | 000                                                                                                                                                                                                                                                                 |

|--------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01     | UU                                                       | 01                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 1      |                                                          |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 1      |                                                          |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 1      |                                                          |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 111    | (000                                                     |                                                                                                                                                         | 001                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 01     | UU                                                       | 01                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 01     | 00                                                       |                                                                                                                                                         | 01                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 01     | 00                                                       |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      | 01                                                                                                                                                                                                                       |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 01     | 00                                                       |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          | 01                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 01     | 00                                                       |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                     |                                                                                                                                                                                                                                                                     |

| 111100 |                                                          | 11110000                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000011 |                                                          | 00001111                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000011 |                                                          | 00001111                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000011 | 00000000                                                 |                                                                                                                                                         | 00001111                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000001 | 000000000                                                |                                                                                                                                                         | 00000111                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000001 | 00000000                                                 |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      | 00000111                                                                                                                                                                                                                 |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000000 | 00000000                                                 |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      | 00000111                                                                                                                                                                                                                 |                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000000 | 00000000                                                 |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          | 00000111                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000000 | 00000000                                                 |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          | 00000111                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                                                                                                                     |

| 000000 | 00000000                                                 |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                          |                                                                                                                                                                    | 00000111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     |                                                                                                                                                                                                                                                                     |