| Last Name: Sample .                                                                                                                                                                                                                                                                                                                                                 | First Name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Student ID:                                                                                                                                                                                                                                                                                                                                                         | Signature:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Course 304-425B (                                                                                                                                                                                                                                                                                                                                                   | Computer Organization and Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $Ap_{i}$                                                                                                                                                                                                                                                                                                                                                            | Final examination ril 19, 2002, 09:00 12:00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Examiner: Prof. V. Hayward                                                                                                                                                                                                                                                                                                                                          | Associate Examiner: Prof. F. Ferrie Lul Leur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FIRST RI                                                                                                                                                                                                                                                                                                                                                            | EAD THESE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>Hand in your signed paper in its entirety</li> <li>Explain every result concisely when as</li> <li>When a numerical answer is asked, alw</li> <li>State any assumption required for an ant</li> <li>Please sign this paper at the top of the p</li> <li>Put your answers in the space provition</li> <li>This exam has 12 pages, 7 sections for</li> </ul> | Calculators and one or two sheets of notes are allowed.  y (along with all signed exam books) at the end of the examination.  ked. Marks will be given for clear, concise solutions.  ways write the formula(s) and then evaluate using the givens.  swer if it is not clear in the text of the question.  bage, write your name and student number legibly there.  ided, answers in any other location will not be marked.  25 questions. Each question is indicated by a bullet sign (•) and  100. You have approximately 180 minutes to complete the exam. |

|                                                                                                                                                                                                                                                                                                                                                                     | PROBLEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SECTIO                                                                                                                                                                                                                                                                                                                                                              | N 1: Performance (5 questions)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| hits. The real machine version A has version B has a split cache that misses are by load/stores instructions and these                                                                                                                                                                                                                                              | nine is 2 when all the memory references, including fetches are cache a unified cache that misses at a rate of 6%. Another real machine at a rate of 5% for instructions and 8% for data. The only data access e form 30% of all instructions. The miss penalty is 20 clock cycles in the between these two machines, all other parameters being equal.                                                                                                                                                                                                       |

| MACHINE A: MISSRATE DATA = Mis                                                                                                                                                                                                                                                                                                                                      | BRATE FETEURS = 0.06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MACHINE B: Miss RATE DATA = C                                                                                                                                                                                                                                                                                                                                       | 1.08; MISSRATE FETCHES = 0.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CPI IDEA = 2 (A) CPIRE                                                                                                                                                                                                                                                                                                                                              | AL= 2+ 0.06 20 + 0.3 0.06 20 = 3.56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Miss PENALTY = 20                                                                                                                                                                                                                                                                                                                                                   | AL= 2+ 0.05 20 + 0.3 0.08 20 = 3.48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| % LD/ST = 30% (B) CPI REA                                                                                                                                                                                                                                                                                                                                           | CPTA = 1.023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| could increase the clock rate by 10%.                                                                                                                                                                                                                                                                                                                               | increasing the depth of its single pipeline from 6 to 9 stages and this. When the processor had 6 stages, the average number of stalls per peline this number increases. What is maximum tolerable average                                                                                                                                                                                                                                                                                                                                                    |

number of stalls per instruction with the 9 stage pipeline to make the effort worthwhile?

$$CC_{q} = CC_{6} \text{ 1.10} \qquad \text{STALL RATE}_{6} = 0.5 \text{ PER INSTRUCTION COUNT, WAITE:}$$

$$GINGLE \text{ PIPE: } CPI_{FOFAL} = 1 \text{ , FOR A SAME INSTRUCTION COUNT, WAITE:}$$

$$\left(1 + 0.5\right) CC_{6} = \left(1 + \text{STALL RATE}_{q}\right) CC_{6} \frac{1}{1.10}$$

$$1.5 \ge \left(1 + \text{STALL RATE}_{q}\right) \frac{1}{1.10} \implies \text{STALLRATE}_{q} \le 1.5 \times 1.10 - 1$$

$$\le 0.65$$

• A floating point application was compiled for a RISC processor having floating point instructions. One run required 20,000 loads/stores, 5,000 branches, 10,000 ALU instructions, 5,000 fixed-point multiplies, 5,000 floating point additions, and 5,000 floating point multiplies. The count of all other instructions was negligible. The application was used to benchmark a machine with floating point hardware. The following CPI's were found: load/stores=2, branches=1.5, ALU=1.2, fixed-point mults=4, FP adds=4, FP mults=8. The same application run on a machine without floating point hardware but which emulated it with integer routines gave: 20,000 load/stores, 8,000 branches, 60,000 ALU instructions, 10,000 fixed-point multiply instructions. The CPI's were almost the same. What is the speed-up provided by the floating point hardware assuming that the clock rates were the same?

FOR A GIVEN SINGLE BENCHMARK, WE CAN SIMPLIFY BY FINDING THE TOTAL NUMBER OF NEEDED CLOCK CYCLES:

$$\#(C_{FP} = 20 \times 2 + 5 \times 1.5 + 10 \times 1.2 + 5 \times 4 + 5 \times 4 + 5 \times 8 = 139.5 \text{ 10}}$$

$$\#(C_{FR} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 60 \times 1.2 + 10 \times 4 = 164 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 2 + 8 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10 \times 10^{3}$$

$$\#(C_{FIX} = 20 \times 1.5 + 10$$

• The compiler for this same processor is now enhanced by a strength reduction optimization feature (e.g. replacing mults by shifts). Now, half of the fixed-point multiplication are replaced by a sequence of 2 ALU instructions. The other effects are negligible. What is the now speed-up provided by the floating point hardware when using this new compiler?

WITH NEW COMPILER, THESE NUMBER BECOME:

#

$$CC_{FP} = 20x2 + 5 \times 1.5 + 12.5 \times 1.2 + 2.5 \times 4 + 5 \times 8 = 132.5 i0^3$$

#  $CC_{FIX} = 20x2 + 8 \times 1.5 + 70 \times 1.2 + 5 \times 4 = 156 i0^3$

#  $CC_{FIX} = 20x2 + 8 \times 1.5 + 70 \times 1.2 + 5 \times 4 = 156 i0^3$

Speedup =  $\frac{156}{132.5} = 1.177$

• We focus now on the performance of a machine with virtual memory and one level of blocking cache. The performance figures are 1 cc hit time and a 5% miss rate for the cache. It takes 30 cc to replace a block. The virtual memory system misses at the rate of 0.0002% and it takes 5,000,000 cc to resolve a page fault. To improve the system, a second level cache L2 is introduced that can replace a L1 block in 10 cc. L2 misses at a rate of 1% and it takes 50 cc to replace a block. What is the speed up introduced by the L2 cache?

BEFORE

HITTIME RATE PENALTY

CACHE I 0.05 SEE MM

LI I 0.05 SEE L2

MM 30

$$210^{-6}$$

$510^{6}$

AMAT =  $140.05(30+10)$

=  $30$

AMAT =  $140.05(30+10)$

AMAT =  $140.05(10+0.01(50+10))$

=  $30$

AMAT =

### **SECTION 2: Integer Pipelining** (4 questions)

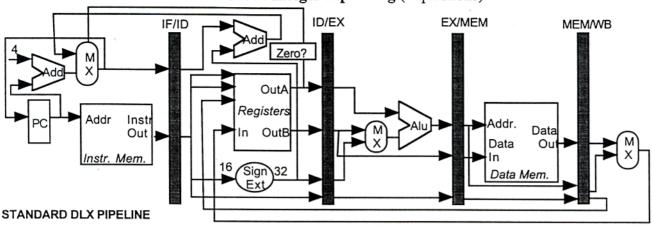

Consider the standard DLX pipe as above and consider it fully bypassed. Recall that basic techniques to handle the branch are "pure delayed branch" and "delayed branch with canceling". Now consider the code sequence:

```

1.

LOOP LW

R2, 0(R3)

\\ load word w

2.

R1, R2, 0

SEQI

R4, R2, x0F \\ set least significant nibble

3.

ORI

BNEZ

R1, OUT

4.

5.

SW

0(R3), R4

\\ store modified w

6.

ADDI

R3, R3, 4

\\ next item

LOOP

7.

\\ jump back

```

• Indicate the 2 instructions after BNEZ and show timing for "delayed branch with canceling" when:

The branch is taken:

|            | The station is taken. |    |    |     |    |     |        |    |    |     |    |  |  |  |  |

|------------|-----------------------|----|----|-----|----|-----|--------|----|----|-----|----|--|--|--|--|

| LW         | エド                    | ID | ΕX | MEM | WB |     |        |    |    |     |    |  |  |  |  |

| SEQI       |                       | IF | ID | 3   | EX | MEM | WB     |    |    |     |    |  |  |  |  |

| ORI        |                       |    | IF | S   | ID | EX  | MEM    | WB |    |     |    |  |  |  |  |

| BNEZ       |                       |    |    |     | IF | ID  |        |    |    | ~   |    |  |  |  |  |

| SW         |                       |    |    |     |    | IF  | CANCEL |    |    |     |    |  |  |  |  |

| INS. @ OUT |                       |    |    |     |    |     | IF     | ID | EX | MEM | WB |  |  |  |  |

#### The branch is not taken:

| LW   | IF | ID | Ex | MEN | WB |     |     |    |     |      |    |  |

|------|----|----|----|-----|----|-----|-----|----|-----|------|----|--|

| SEQI |    | IF | ID | 5   | EX | MEM | WB  |    |     |      |    |  |

| ORI  |    |    | IF | S   | ID | Ex  | MEM | WB |     |      |    |  |

| BNEZ |    |    |    |     | IF | ID  |     |    |     |      |    |  |

| SW   |    |    |    |     |    | IF  | ID  | EX | MEM | WB   |    |  |

| ADDI |    |    |    |     |    |     | IF. | ID | EX  | MEIT | WB |  |

• For pure branch delay, does the code execute correctly? If yes, state why. If not, place NOP(s) to restore correctness. Ignore the J instruction and apply no other transformation.

LW SEGI ORIZ BNEZ NOP SW ADPI

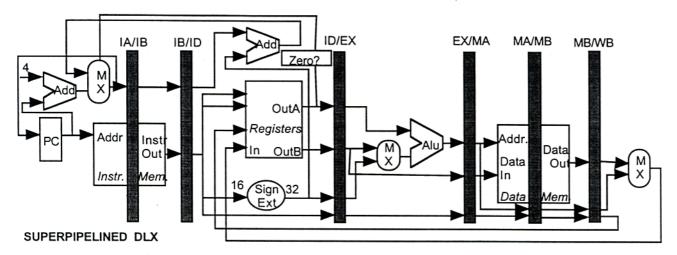

Consider now a superpipelined version of DLX designed in an effort to increase the clock rate (memory accesses are performed in two cc instead of one). Like the standard version, it is fully bypassed, including the data memory, and branches are handled by delayed branches with canceling.

• Using timing diagrams, determine by how much the clock rate should be increased to make the enhancement worthwhile for this sequence of code (it does string copy):

LOOP: LB R1, 0(R2)

SB 0(R3), R1

BEQZ R1, OUT

ADDI R2, R2, 1

ADDI R3, R3, 1

J LOOP

LOOP // J is folded, so its CPI=0

Standard DLX / MEM WB SB Eχ ID TEN WB ID BEGZ IF IF ID MEM WB ADDI EX ADDI IF ID EX MEM

Superpipelined DLX LB IB MA WB SB EX MB WB TA IB ID MA TA #B EX MA MB WB BEGZ ID TA ADDI  $\mathcal{I}\mathcal{B}$  $\mathcal{I}\mathcal{D}$ EX MA MB WB MA TA IB ID ADDI

Calculate here the minimum required clock rate improvement to make the superpipelined design worthwhile?

7/6 SINCE SUPERPIPELINING TAKES 7CC TO EXECUTE VS. 6 CC

Schedule this code for the superpipelined case and state why you could use speculative execution, or why

you could not:

IT'S POSSIBLE TO SPECULATURLY "ADDI R2" AND FILL THE LOAD DELAY SLOT. THE OTHER ADDI CAN FILL THE BRANCH DELAY SLOT (COULD USE SB TOO).

LOOP: LB RI, O(RZ)

ADDI RZ, RZ, I

SB O(R3), RI

BEOZ RI, OUT

ADDI R3, R3, I

IT CAN BE VERIFIED THAT

THIS WORKS, BUT THE

TWO BRANCH DELAY SLOT CAN

BE ARGUED TO BE PROBLETATIC.

END OF SECTION 2 (4 questions, 9/25 so-far)

# **SECTION 3: Loop Transformations With FP Code (3 questions)**

The FPUs are fully pipelined and bypassed. In case of write contention (one write per clock cycle) the earliest instruction has priority and stalls the contending instruction(s). Assume the following data:

```

Instruction producing result

Instruction using result

Latency in clock cycles

Load double

any FPU operation

completion of any FPU operations

Store Double

0

FP ADD

FPU operation

3

FP MULT

FPU operation

4

DELAYS

F2, 0(R1)

LOOP: LD

A[I] = A[I] * c

MULTD F2, F2, F0

F2, 0(R1) 4

SD

LD

F4, 0(R2)

B[I] = (A[I] + B[I])

ADDD

F2, F2, F4

F2, 0(R2)^{4}

SD

ADDI

R1, R1, 8

INTEGER

ADDI

R2, R2, 8

INDEX AND

ADDI

R5, R5, -1

LOOP

BNEZ R5, LOOP

CONTROL

```

• Schedule this loop taking advantage of software pipelining to minimize stalls, but use no other transformation. For conciseness, ignore the init and cleanup code. Assume that, due to prediction, there is no branch delay.

```

SP

F2, -8(R2)

USE SD FROM PREVIOUS

LD.

F2, O(R1)

TTERATION AND INTEGER

F2, F2, F0

MULTO

CODE TO FILL DELAYS.

RI, RI, 8

APDI

ABSENCE

OF RENAMON G

DELAYS

ADDI

R2, R2, 8

LIMITS THE OPTIONS.

R5, P5, -1

ADDI

OTHER

POSSIBLE SOLUTION STARTS LIKE:

LD

F4, -8(RZ)

SD F2

SD

F2, -8 (Ri)

F2

LD

ADPD

F2, F2, F4

LP F4

BNE)

R5, 2007

```

• Unroll this loop twice (that is, one interation for I and I+1), and schedule it to minimize stalls. FIRT UNROLL AND RENAME THEN

```

FZ, O(RI)

F2, O(RI)

LD

LD F8, B(RI)

MU4D F2, F2, F0

SD F2, O(R1)

MOLTD F2, F2, F0

MULTD F8, F8, F0

F4, O (R2)

APDD F6, F4, F2

LD

F4, O(RZ)

LD

F6, O (R2)

Flo, 8(R2)

//FREE F2

F8, 8 (RI)

ADDIT

R5, R5, -2

WE NOW HAVE

MULTO F8, F8, FO

ADDO F6, F2, F4 // MULTO'S DONE

PARALLEL CODE

ADDD F12, F8, F10 / START ADDD'S

SD F8, 8(R1)

LD F10, 8(R2)

SO WE CAN

FZ 10(A1) /1 STORE HOUTD'S

SD

OVERLAP TWO

ADD F12, F8, F10

F8, 8(RI)

SD

TTERATIONS

F6, O(R2) // STORE APODS

SD

F12, 8(R2)

F/2,0(R2)

LOTS OF OTHER

APRI

R1, R1, 16

ADDI RI, RI, 16 11 POINTERS

ADDI

RZ, RZ, 16

OPTIONS FOR A

APDI R2, R2, 16

BNE2 R5, LOOP // NO DELAY

APIT

R5, R5, -2

GOOD SCHEDULE!

BNEZ

LOOP

```

SCHEDULE

• Consider computing the dot product of vectors stored in two arrays as in:

```

Loop LD

F2, 0(R1)

// A[I]

F4, 0(R2)

_{

m LD}

// B[I]

MULTD F2, F2, F4

// A[I] * B[I]

ADDD F0, F0, F2 4

// P += A[I] * B[I]

R1, R1, 8

ADDI

// I = I + 1

ADDI R2, R2, 8

ADDI R3, R3, -1

BNEZ R3, Loop

```

• Schedule it for a VLWI processor that has the following structure (use the same latencies).

| Memory Ref 1 | Memory Ref. 2 | FP Op 1          | FP Op 2         | Integer Op/branch |

|--------------|---------------|------------------|-----------------|-------------------|

| LD F2, O(R1) | LD (F4,0(RZ)  |                  |                 |                   |

|              |               |                  |                 | APDIE RI, RI, 8   |

|              |               | MULTD F2, F2, F4 |                 | ADDI R7, R2, 8    |

|              |               |                  | -               | APPI R3, R3, -1   |

|              |               |                  |                 |                   |

|              |               |                  |                 |                   |

|              |               |                  |                 |                   |

| , .          |               |                  | APRD FO, FO, F2 | BNEZ R3, LOOP     |

COMMENT: AS EVIDENCED BY THIS EXAMPLE, WINT PROCESSIONS PERFORM

POORLY WITHOUT HEAVY CODE TRANSFORMATION.

END OF SECTION 3 (3 questions, 12/25 so-far)

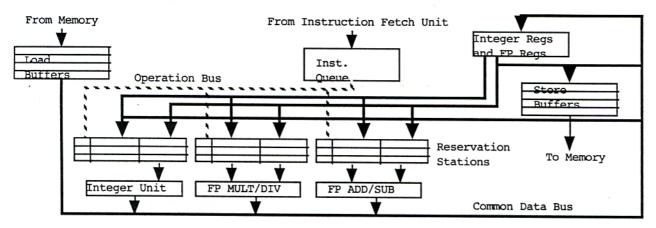

### **SECTION 4:Tomasulo's Algorithm** (4 questions)

Consider the pipeline below. The integer unit can be controlled to carry out any type of integer instructions. It has one FP ADD/SUB unit and one MULT/DIV unit. The load and store buffers have four entries each. The reservation stations have three entries.

Assume that the latencies are 0 for all integer operations, 1 for loads, 4 for the FP add/sub's, 6 for the multiplication and 12 for the divides, regardless of the instruction using the result. All units are fully pipelined. The Common Data Bus is written at the end of the last clock cycle of an operation. An operation that depends on the written value starts at the next clock cycle. The Common Data Bus can support multiple data transfers. Assume that a new instruction is fetched at each clock cycle and is issued at the next clock cycle if there is free entry in the reservations or in the buffers.

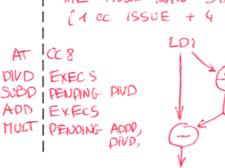

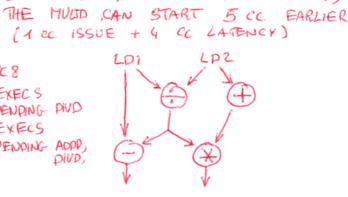

• By inspection of the code sequences A and B (watch for the SUBD) and by completing the timing tables, determine the case in which the second SD completes first and state why, assuming that all the reservations stations and the store buffers are initially free.

| Fetch | Code  | A          | Issue | Exec  | Write CDB |

|-------|-------|------------|-------|-------|-----------|

| CC1   | LD    | F2. 0(R1)  | CC2   | 3-4   | CC4       |

| CC2   | LD    | F4. 0(R2)  | CC3   | 4-5   | CC5       |

| CC3   | DIVD  | F6. F2. F4 | CC4   | 6-18  | CC18      |

| CC4   | SD    | 0(R1), F6  | CC5   | 19    |           |

| CC5   | SUBD  | F6. F2. F6 | CC6   | 19-23 | cc23      |

| CC6   | ADDD  | F4. F4 F4  | CCT   | 8-12  | cel2      |

| CC7   | MULTD | F2. F4. F6 | CC8   | 24-30 | cc30      |

| CC8   | SD    | 0(R2). F2  | ccq   | 31    |           |

| Fetch | Code 1 | В    |     |     | Issue      | Exec  | Write CDB |

|-------|--------|------|-----|-----|------------|-------|-----------|

| CC1   | LD     | F2.  | 011 | (1) | CC2        | 3-4   | CC4       |

| CC2   | LD     | F4.  | 0(F | 22) | CC3        | 4-5   | CC5       |

| CC3   | DIVD   | F6.  | F2. | F4  | CC4        | 6-18  | CC18      |

| CC4   | SD     | 0(R) | ۱). | F6  | CC5        | 19    |           |

| CC5   | SUBD   | F2.  | F2. | _F6 | CC6        | 19-23 | cc23      |

| CC6   | ADDD   | F4.  | F4  | F4  | CC7        | 8-12  | ce12      |

| CC7   | MULTD  | F2.  | F4. | F6  | $\alpha s$ | 19-25 | CE25      |

| CC8   | SD     | 01R2 | 2١. | F2  | ccq        | 26    |           |

| Comments HERE | {DIVD > SUBD & MULTD

SO THERE IS MORE PARALLELISM,

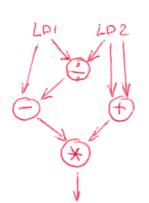

Comment DATA DEPENDENCIES ARE SUCH DIVD -> SUBD -> MULTO SO ALL THE LATENCIES APD UP. COMPLETE DATA FLOW DIAGRAM IS:

7

Use "Mem[Reg[R1]]" to denote, for example, the *value* fetched by the first load, "Reg[R1]" to denote the *value* held in register R1, and #8 to denote the value 8.

• Indicate in the tables the state of the reservation stations and of the registers at clock cycle 8 for code B only:

| Name       | Busy | Op.   | Vj            | Vk            | Qj        | Qk         |

|------------|------|-------|---------------|---------------|-----------|------------|

| MULT/DIV-1 | V    | DIVD  | MEN [REG[RI]] | MENTREGERZZ   | _         | _          |

| MULT/DIV-2 | V    | MULTO |               | _             | ADD/SUB-2 | MULT/DIV-1 |

| MULT/DIV-3 |      |       |               |               |           | 1000,7700  |

| ADD/SUB-1  | V    | SUBD  | MEM [REG[AI]] | _             | _         | MULT/DIV-1 |

| ADD/SUB-2  | V    | APPP  | TEN [REG[R2]] | MERCIREGERZI] |           | _          |

| ADD/SUB-3  |      |       |               |               |           |            |

| INT-1      |      |       |               |               |           |            |

| INT-2      |      |       |               |               |           |            |

| INT-3      |      |       |               |               |           |            |

| Field | F0 | F2        | F4        | F6         | F8 | R1 | R2 | R3 | R4 |

|-------|----|-----------|-----------|------------|----|----|----|----|----|

| Qi    |    | ADD/SUB-2 | ADD/SUB-2 | MULT/DIV-1 |    |    |    |    |    |

What is the estimated throughput measured in number of floating point instructions per second when the

architecture on the previous page repeatedly executes the code below (a loop unrolled a large number of

times)? Assume same behavior, perfect cache performance, and absence of structural hazards such as shortage

of reservation station entries.

```

IF THE ADDI'S WERE BETWEEN THE

. . .

. . .

SD'S AND LD'S, THEN THE CODE WOULD

LD

F2, 0(R1)

BE PARALLEL AND HENCE LIMITED BY

LD

F4, 0(R2)

STRULTURAL LIMITATIONS SUCH AS FETCH RATE

SUBD F6, F2, F4

ADDD

F8, F2 F6

HOWEVER, EACH NEW CALCULATION PEPENPS

ADDI

R1, R1, 8

ON THE PREVIOUS ONE SO WE MUST

MULTD F2, F4, F4

ADDI R2, R2, 8

ESTIMATE THE TOTAL LATENCY.

0(R1), F8

SD

SD

0(R2), F2

LD

F2, ...

\\ again and again

LD ...

. . .

```

THERE ARE TWO PARALLEL CALCULATIONS, HULTD AND SUBD - ADDD, BOTH TAKE ABOUT 14 CLOCK CYCLES TO COMPLETE BEFORE A NEW SEQUENCE CAN START. SO WE HAVE ABOUT B FLOPS PER 14 CC OR 1 FLOP PER 4.6 CC.

### **SECTION 5: Branch predictors** (2 questions)

• A machine has a 2-bit branch predictor. Estimate how many correct and how many incorrect predictions are made while executing the code below per outer iteration, assuming a 100% hit rate and no clashes in the predictor table (Giving just a number will earn you no marks, do not mind the nonsensical computation).

```

for(;;) {

/* begin for ever */

i = 0;

do {

++i;

i = 0:

do {

if (j == 10 \mid | j == 20) /* call it B1 */

A[i] = j;

} while (j < 100);</pre>

/* call it B2 */

\} while (i < 4);

/* call it B3 */

/* end for ever */

BEHAVIOR

CORRECT 2 INCORRECT

Bi

T---TNT--TNT--TT. 98

B2

BEHAVIOR

3 CORRECT 1 INCORRECT

B3 BEHAVIOR

TOTAL: 791 CORRECT PREDICTIONS AND B MISPREPICTIONS

```

• Assume now that a machine as a (1,1) correlating predictor. What is its performance when executing the code below? Report performance in the same manner as above (same remarks).

```

for(;;) {

/* begin for ever */

i = 0;

while (i < 100) {

/* call it B1 */

if (i % 2 == 0)

/* call it B2 */

A[i] = 0;

else

A[i] = 1;

++i;

}

}

/* end for ever */

A PAIR OF 1 BIT PREDICTORS, CALL THEM PO/PI.

PO IS USED WHEN THE LAST BRANCH WAS TAKEN AND PI WHEN IT WAS NOT.

TEST ALL CASES.

WORK A FEW FTERATIONS TO

COMMENT:

BI ALWAYS CORRECTLY

B2 B1 B2 B1 B2

END OF SECTION 5 (2 questions, 18/25 so-far)

```

#### **SECTION 6: Loop level parallelism (3 questions)**

· Consider this loop and list all the dependencies: true data dependencies and name dependencies; and whether they are loop carried.

```

for (i = 0; i < 100; ++i) {

c[i] = a[i] + c[i];

/* S1 */

b[i] = c[i + 1] + a[i];

/* S2 */

c[i + 1] = a[i + 1] + a[i + 1]; /* S3 */

a[i + 1] = b[i + 1] + b[i + 1]

/* S4 */

}

OUTPUT-DEPENDENCIES

DEPENDENCIES

ANTI-DEPENDENCIES

SZ DEPENDS ON S3

DEPENDS ON S3 (LC)

S3 DEPENDS ON SI (LC)

11 34

S3

S4 (Le)

51

16

11 51 (20)

92

S4 (Le)

S2

11 S2 (Le)

ll

84

```

# LC: LOOP CARRIED

Use software renaming and/or other transformation(s) so that it becomes parallel:

```

BRUTE FORCE SOLUTION:

XE0] = T[0] + Z[0]X

RENAME ALL MARIABLES

Y[0] = C[1]+T[0]

INVOLVED IN NAME DEPENDENCES,

THEN START LOOP AT S3

FOR(i=1; i<100; ++i){

SINCE NO DATA PEPENDENCY

Z[i] = \alpha[i] + \alpha[i]

BETWEEN 93 AND SZ.

T[i] = b[i]+ b[i];

X[i]= T[i]+Z[i]

X[i]=T[i]+Z[i];

Y[i] = c[i+i] +T[i]

Y[i] = c[i+i]+ T[i];

Z[4] = a[i+i]+a[i+i]

T[i+i] = b[i+i] + b[i+i]

251007= 95100]+ 95100];

T[100] = b[100] + b[100];

```

```

SOLUTION &

LEAST EFFORT

ONLY

NOTICED THAT THE

NAME DEPENDENCY & BETWEEN

RENAME

S3 AND S2 AND

dost C.

C[0] = a[0] + C[0]

b[0] = X [1] + 9[0]

FOR (i=1; 1/100; ++i) {

Csi]= asi]+asi]

9[i] = b[i] + b[i]

cli] = ali] + cli]

b[i] = x[i+1] + a[i]

C[100] = a [100] + a [100];

9[100]= 6[100]+ 6[100];

```

• Can this loop be transformed to become parallel. Why or why not?:

```

for (i = 1; i < 100; ++i) {

a[i] = a[i - 1] + a[i];

/* S1 */

b[i] = a[i] + a[i + 1];

/* S2 */

}

```

DATA DEPENDENT ON SI, SO THEY CANNOT RUN IN PARALLEL. SZ IS LOOP-CARRIED DEPENDENT ON SI, SO ONE ITERATION MUST TERMINATE BEFORE ANOTHER ONE CAN START, NO PARALLELISM.

# **SECTION 7: Memory Hierarchy** (4 questions)

37

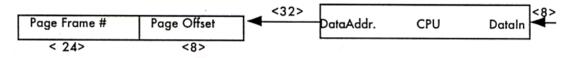

Consider the organization of the Cheap'O computer memory hierarchy. Notice that the CPU produces 15 bit virtual addresses and the memory is byte addressed. A "load byte" instruction requests the byte stored at address "0A1B 2C08". From the content of the TLB, and of the cache, determine the value of the byte that is returned.

• As the request works its way through the hierarchy, specify the values of

1. Data Address

0A1B 2C08

2. Page frame #

DA 1B2C

3. Page Offset

08

(PHYS ADDR. EFO8)

4. Cache Tag

EFO

5. Cache Index

$(10)_{i} = 2$

6. Cache Block Offset

(00), = 0

7. Byte returned

CASSUMING THIS BYTE NUMBER ING !

CC DD EE FF

| V R W |   | W | Tag    | Phys. Frame # |                     |

|-------|---|---|--------|---------------|---------------------|

| 1     | 1 | 1 | 987654 | 23            |                     |

| 1     | 1 | 1 | FABBAF | 89            | Translation         |

| 1     | 1 | 1 | OA1B2C | EF            | Lookaside<br>Buffer |

| 1     | 1 | 1 | BOAC55 | 01            |                     |

|       |   |   | <24>   | <8>           | •                   |

| Cache Address Format |       |                 |  |  |  |  |  |  |  |  |

|----------------------|-------|-----------------|--|--|--|--|--|--|--|--|

| Tag                  | Index | Block<br>Offset |  |  |  |  |  |  |  |  |

| <12>                 | <2>   | <2>             |  |  |  |  |  |  |  |  |

|       |   | Tag | Data     | ٧ | Tag | Data     | _ | ٧ | Tag | Data     | ٧ | Tag | Data     |

|-------|---|-----|----------|---|-----|----------|---|---|-----|----------|---|-----|----------|

| Set-0 | 1 | 012 | 00112233 | 1 | CDE | CCDDEEFF |   | 1 | 89A | 8899AABB | 1 | 456 | 44556677 |

| Set-1 | 1 | 345 | 44556677 | 1 | F01 | 8899AABB |   | 1 | BCD | 00112233 | 1 | 789 | CCDDEEFF |

| Set-2 | 1 | 678 | 8899AABB | 1 | 234 | 44556677 |   | 1 | EF0 | CCDDEEFF | 1 | ABC | 00112233 |

| Set-3 | 1 | 9AB | CCDDEEFF | 1 | 567 | 00112233 |   | 1 | 123 | 44556677 | 1 | DEF | 8899AABB |

Set Associative Cache (4 sets of 4 blocks)

"Cheap'O Computer" micro-architecture, memory hierarchy, Version 2, Rev. 5

In robotics and graphics, a common case is the product of a vector by a 4x4 matrix that can be coded as follows. Whether this is coded inline as shown, or as nested loops, has no bearing on the answer since, in this question, we are interested in cache operation. (p, a and T are floats).

```

p[0] = T[0][0] * a[0] + T[0][1] * a[1] + T[0][2] * a[2] + T[0][3] * a[3];

p[1] = T[1][0] * a[0] + T[1][1] * a[1] + T[1][2] * a[2] + T[1][3] * a[3];

p[2] = T[2][0] * a[0] + T[2][1] * a[1] + T[2][2] * a[2] + T[2][3] * a[3];

p[3] = T[3][0] * a[0] + T[3][1] * a[1] + T[3][2] * a[2] + T[3][3] * a[3];

```

The compiler arranges the elements of the matrix row-wise such that T[i][j] is contiguous to T[i][j+1]. Suppose also that the cache blocks are just four floats long and that data is properly aligned. Assume that:

- 1. there is no conflict replacements.

- 2. the cache is "write through",

- 3. it is "no-allocate".

- 4. it is blocking,

- The hit-time is 1 CC and the penalty (b \* 4), where b is the block size in floats. The cache is just big enough to hold 32 floats. Would it better to have 8 blocks of 4 floats, or 4 blocks of 8 floats? Justify your answer quantitatively.

CASE 8x4: WHEN TEOTED IS LOADED, A ROW IS LOADED IN ONE BLOCK WHEN A [0] IS LOADED, VECTOR Q IS LOADED IN A SECOND BLOCK THEN, T[1][0], T[2][0], AND T[3][0] ALLOCATE 3 MORE BLOCKS.

TOTAL 32 ACCESSES WITH 5 PENALTIES: 32+5x16=1/2 CC TO PERFORM ACCESS TO MULTIPLY CASE 4X8 ! WHEN TEOTED IS LOADED, TWO ROWS ARE LOADED IN ONE BLOCK WHEN a [0] IS LOADED, VECTOR a IS LOADED IN A BLOCK THEN TOTALLOCATE ONE MORE BLOCK FOR TWO ROWS

TOTAL 32 ACCESSES WITH 3 PENALTIES: 32+3x32=128CC TO PERFOR SAME WITH BE OF

• For the case of 8 blocks of 4 floats, which of these two improvements would be preferable: reducing the penalty to 6 CC by adding a non-blocking feature, or making the cache "write allocate"?

FIRST EN HANCEMENT: 32+5×6=62 CC FOR REAPS SECOND ENHANCEMENT CAUSES AN EXTRA PENALTY WHEN PLOT IS WRITTEN , SO COUNTING THE WRITES : 36+6×16= 132 CC.

IT IS UNLIMELY THAT 4 WRITES ARE WORTH TO CC. THIS IS DUE TO THE FACT THAT THERE ARE MANY MORE READS THAN WRITES.

- Answer these yes/no questions

- "A reorder buffer" is a method to reduce the miss penalty in caches

♦ "A reorder butter" is a method to reduce the imas points, ...

♦ "Blocking in matrix computations" is used to minimize the number of page faults [yes/no]: NO (BLOCKING AT CHARLES TO (BUT APPLIES TO ) • "Protection" is a software technique to speed up recursive code [yes/no]: NO

♦ "A write buffer" makes it possible to pipeline block replacement in caches

VH AS WELL]

[yes/no]: NO

END OF SECTION 7 (4 questions) and END OF EXAM (and end of the 25 questions)