| Last Name:  | SAMPLE | First Name: |  |

|-------------|--------|-------------|--|

|             |        |             |  |

| Student ID: |        | Signature:  |  |

### Course 304-425B -- Computer Organization and Architecture

Final examination

April 18, 2000, 9:00 -- 12:00

Examiner: Prof. V. Hayward

Associate Examiner: Prof. K. Khordoc

### INSTRUCTIONS

- This is a closed book examination. Calculators and up to two sheets of notes are allowed.

- Explain every result concisely when asked. Marks will be given for clear, concise solutions.

- State any assumption required for an answer if it is not clear in the text of the question.

- This exam has 12 pages including this one. It has 7 sections for 24 questions (including a bonus question) indicated by the bullet sign (•). The marks add up to 100.

- Please sign this paper at the top of the page, write your name and student number legibly there.

- Put your answers in the space provided and keep all the pages together.

#### PLEASE NOTE CAREFULLY

- Make sure that the signed paper in its entirety is handed in (along with all signed exam books) at the end of examination.

- Make sure that the answers are put in the space provided, answers in any other location will not be marked.

- You have approximately 180 minutes to complete the exam.

## Section 1: Performance (12 points)

Apply Amdahl's law to compute the speed-up factor for a machine to which an enhancement is added to improve some mode of execution by a factor 10. This mode is used 50% of the time, measured as a percenta (4 points) of the original exec time.

Te = Tu

$$\left[ (1 - FE) + \frac{FE}{SUE} \right]$$

Su =  $\frac{Tu}{Te} = \frac{1}{(1 - FE) + \frac{FE}{SUE}} = \frac{1}{.5 + \frac{.5}{10}} = \frac{1}{.55} = 1.82$

Derive a variant of Amdahl's law to compute the speed-up factor for a machine to which an enhancement is added to improve some mode of execution by a factor 10. However in this question, the mode is used 50% the time measured as a percentage of the enhanced exec time.

Hint: start from the definition of speed\_up =  $\frac{ExecTime_{unenhanced}}{ExecTime_{enhanced}}$ , in short:  $SU = \frac{T_u}{T_e}$ .

$$SU = \frac{Tu}{Te} = \frac{1}{Te} Te \left[ (1 - FE) + FE SUE \right]$$

$$= .5 + .5 = 5.5$$

Assume that we have a Load/Store machine which behaves with a perfect cache as follows:

1 clock cycle 40% ALU ops 2 clock cycles

30% Load/Stores 2 clock cycles 30%

Branches and others The machine is modified to add new ALU instructions that have one source operand in memory. These new register-memory instructions have a clock cycle count of 2. The total number of ALU operations, branches, ar others instruction remains the same, of course, but the number of loads and stores is divided by two. Is this enhancement worth implementing?

instruction remains the same, of course, but the number of loads and stores is divided by two. Is the cement worth implementing?

$$\frac{CPU_{TINE}}{CC} = \frac{TC}{C} \sum_{i} F_{i} CPI_{i} \qquad \text{S.I. } \sum_{i} F_{i} = I \qquad IC, CLASSES, CPI'S CHAN$$

NEW CLASSES : ALUOP, ALUOP2 1/5 80 NEW CPT'S : 1 2 2 2 NEW Fi'S : 4-.15 ./5 ./5 ./5 .85 NEW FC : .85 ICOLD

TIME NEW = .85 (.25 + .15 x2 + .15 x 2 + .3 x2) = 1.45

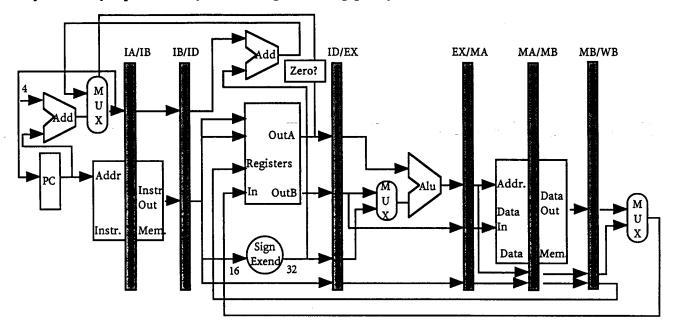

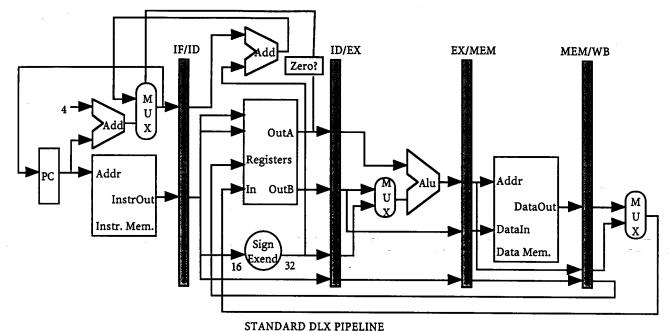

Timing analysis reveals that the memory cycles in the standard DLX pipeline are the limiting factor for clock c time improvement. One design option is to split the memory cycles in an attempt to increase the clock rate. Th often called super pipelining and is illustrated in the diagram below. Complete instruction fetches takes two standard IB. In the first stage, the memory addressed is specified, in the second, the instruction is read out. same technique is applied to the MEM stage, now split into a MA and a MB stage. The new design is fully pipeli. This is symbolically represented by introducing two new pipe registers.

SUPERPIPELINED DLX

• Assuming full bypassing/forwarding (including to and from the memory) use the chart below to report timing diagram for this code. Also note that the branch must stall. Show the branch behavior to be delibranch. Suppose that the jump instructions benefit from branch folding and that there is a hit. (10 points)

| LOOP: | LW   | R1, 0(R2) |

|-------|------|-----------|

|       | SW   | R1, 0(R3) |

|       | BEQZ | R1, OUT   |

|       | ADDI | R2, R2, 4 |

|       | ADDI | R3, R3, 4 |

|       | J    | LOOP      |

|       |      |           |

OUT: ....

| LW   | IA | IB | ID | EX        | HA | MB | WB |     |    |     |    |    |    |    |    |    |  |  |  |

|------|----|----|----|-----------|----|----|----|-----|----|-----|----|----|----|----|----|----|--|--|--|

| SW   |    | IA | IB | <b>FD</b> | EX | S  | MA | πB  | WB |     |    |    |    |    |    |    |  |  |  |

| BEQZ |    | -  | TA | TB        | 5  | 5  | ID | Ex  | MA | 11B | WB |    |    |    |    |    |  |  |  |

| ADDI |    |    |    | TA        | క  | 3  | IB | ID  | EX | MA  | nB | WB |    |    |    |    |  |  |  |

| ADDI |    |    |    |           |    |    | IA | IB  | ID | EX  | HA | MB | WB |    |    |    |  |  |  |

| J    |    |    |    |           |    |    |    | IA  | IB | ,ID |    |    |    |    |    |    |  |  |  |

| LW   |    |    |    |           |    |    |    | DX. | 被  | 'ID | EX | MA | MB | WB |    |    |  |  |  |

| SW   |    |    |    |           |    |    |    |     | IA | IB  | ID | EX | S  | MA | MB | WB |  |  |  |

.

Recall that there are four basic techniques to handle branches in a pipeline like DLX's:

(A) flush (or freeze) a number of instructions after the branch; (B) static prediction such as "predict-not-taken (C) delayed branch which creates "delay slots"; (D) delayed branch with canceling.

Consider now the following sequence to compute the double of the absolute value of a number in memory:

```

1.

\\ load number

LW

R2, 0(R3)

2.

SLTI R1, R2, 0

\\ R1 <-- 1 if a < 0

3.

BEQZ R1, SKIP

\\ skip if a > 0

4.

R2, R0, R2

SUB

\\ negate

5.

\\ double

SKIP:

ADD

R2, R2, R2

SW

0(R3), r2

\\ store back

```

Show the timing of this sequence for the DLX pipeline assuming full forwarding and bypassing hardware assuming a register read and a write in the same clock cycle implicitly "forwards" through the register file (refirst and then read). Use the chart to show the timing of instructions starting at instruction SLTI when the brais taken. Fill-in the two blank entries according to the case. (note: a similar question was given last term, however is NOT the same question).

### (B)"predict-not-taken":

(5 points)

| LW   | IF | ID | EX | NE | WB |    |    |    |    |    |    | [ |  |  |  |

|------|----|----|----|----|----|----|----|----|----|----|----|---|--|--|--|

| SLTI |    | TF | ID | S  | EX | NE | WB | -  |    |    |    |   |  |  |  |

| BEQZ |    |    | IF | 5  | S  | ID | Ex | ΠE | WB |    |    |   |  |  |  |

| 808  |    |    |    |    |    | IF | ID |    |    |    |    |   |  |  |  |

| ADD  |    |    |    |    |    |    | TF | ID | Ex | ne | WB |   |  |  |  |

```

C). Schedule the following code, to minimize the stalls.

(5 points):

LOOP: SGT R4, R1, R6

BNEZ R4, OUT

\\ compare R1 with R6

1.

2.

\\ if R1 > R6

→ LW

\\ Load number

R2, 0(R3)

3.

SLTI R4, R2, 0

4.

\\ skip if a > 0

5.

BEQZ R4, SKIP

SUB

R2, R0, R2

\\ negate

6.

7.

SKIP:

ADD

R2, R2, R2

\\ double

ADDI R3, R3, 4

\\ increment pointer

8. --

9.

SW

0(R3), r2

\\ store back

\\ increment counter

\\ loop back to while test

10.

ADDI R1, R1, 1

LOOP

11.

R2, R0, R0

12.

OUT:

AND

\\ clear R2

ATA

HAZARD

(DELAYED BRANCH): BOK, E NEEDS

DELAY

BRANCH

HAZARD

LOAD

THE SLOTS | E.G.

TO

FILL

STRATE SIES

MANY

"ADDI'S

UP

THE

ROVE

"LOAD"

BEFORE

BNEZ : FILLS

1w0

THE

ROVE

BEFORE

BNE 2

THE

MOVE

SLOT (KNOWLEPGE

OF SETANT

12

PELAY

NUMBER

DOUBLE

EXAMPLE

R4, R1, R6

SGT

LOOP:

LOAD NUMBER

REGARDLESS OF

Re, o(R3)

LW

BRANCH OUT COI

R4, OUT

BNEZ

SLTI

R4, R2, Q

PO TEST IN

DELAY SLOT

R3, R3,

ADDI

FILL WITH

APDI

R4 , SKIP

BEQZ

RI, RI, I

APPI

FILL

SLOT

APPI

WITH

R2, Ro, R2

SUB

R2, R2, R2

SKIP:

ADD

O(R3), R2

SW

J

LOOP

```

Assuming now that the machine can detect nazards, has forwarding nardware, and uses delayed branches (c

R2, RO, RO

AND

OUT:

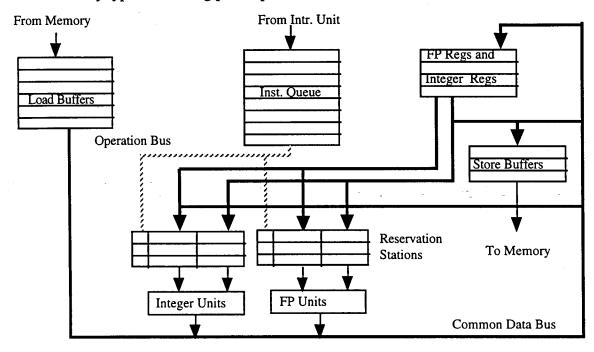

Consider the pipeline below. The integer units can be controlled to carry out any types of integer instructions an the FP units any types of floating point operations.

| LOOP: | LD    | F2,0(R1)     |

|-------|-------|--------------|

|       | MULTD | F4,F2,F0     |

|       | LD    | F6,0(R2)     |

|       | ADDD  | F6,F4,F6     |

|       | SD    | 0(R2),F6     |

|       | ADDI  | R1,R1,#8     |

|       | ADDI  | R2,R2,#8     |

|       | SGTI  | R3,R1,200012 |

|       | BEQZ  | R3,LOOP      |

Consider the code at the left which implement the vector operation: Y = a \* X + Y where X and Y are vector arrays.

Assume the latencies are 0 for all integer operations including loads, 4 for additions, 6 for the multiplication regardless of the instruction using result. The Common Data Bus is written and read on the same cycle and support multiple data transfers (so there is no structural hazard there).

Use "Mem[10+Reg[R1]]" to denote, for example, the *value* fetched by first load, "Reg[R1]" to denote the *value* to be held in register R1, and to denote the value 8.

To illustrate operation, the table below indicates the status of the pipeline once the instructions of the first iterati have issued (that is at clock cycle 8), starting from a blank state.

| Instruction | on Status including the CC collissue | Execute    | Write Result |

|-------------|--------------------------------------|------------|--------------|

| LD          | 1                                    | 2          | 3            |

| MULTD       | 2                                    | 37         | 8            |

| LD          | 3                                    | 4          | 5            |

| ADDD        | 4                                    | 8?? 4 - 10 | ?? 11        |

| SD          | 5                                    | ?? 🕻       | ??           |

| ADDI        | 6                                    | 7          | 8            |

| ADDI        | 7                                    | 8          | ?? 9         |

| SGTI        | 8                                    | ? <b>q</b> | ?? <b>10</b> |

# CALL

Indicate in the table below the state of the reservation stations.

(4 points)

|                   |             |       | Reserv     | vation Stations | 0:        | Qk |

|-------------------|-------------|-------|------------|-----------------|-----------|----|

| me                | Busy        | Op    | Vj         | Vk              | <u> </u>  | QK |

|                   | <u> </u>    | HULTO | MEM O+ REG | [RIJ] REGIFO    |           |    |

| U <u>1</u><br>U 2 | <del></del> | ADDD  |            | MEN TO+REG S    | R2]] FPUI |    |

|                   | <u> </u>    | ADDI  | REGERIZ    | #8              |           |    |

| 7 1               | ~           | ADDI  | BE4[85]    | #8              | 1.5511    |    |

| 3                 | Y           | SCTI  |            | Þo∦₹            | INTUL     |    |

| <u> </u>          |             | Note  |            |                 |           |    |

Indicate in the table below the status of the registers.

(2 points)

| Register Status   R1   R2   R3       R1   R2   R3     R2   R3   R3   R4   R5   R5   R5   R5   R5   R5   R5 |       |    |     |      | Register | Status |      |          |  |

|------------------------------------------------------------------------------------------------------------|-------|----|-----|------|----------|--------|------|----------|--|

| Field FO 12 1/173                                                                                          |       | Ε0 | EO  | F4   | E6       | Rl     | R2   |          |  |

|                                                                                                            | Field | FU | 1.7 | EDUI | €PU 2    | INT    | INT2 | <u> </u> |  |

Indicate in the table below the state of the store buffers

(2 points)

|         | Store    | Buffers | g. 2    |

|---------|----------|---------|---------|

| Field   | Store 1  | Store 2 | Store 3 |

| ieid    | FPU 2    |         |         |

| usy     | - Y      |         |         |

| Address | 0 + [R2] |         |         |

Ignoring the branch delay, now show the new state of the machine, one clock cycle later (this means a new load has been issued).

Indicate in the table below the state of the reservation stations.

(4 points)

| ne                   | Busy                                  | Op   | Vj       | Vk              | Q] | Qk |

|----------------------|---------------------------------------|------|----------|-----------------|----|----|

|                      | <u> </u>                              | ADDD | REG[F4]  | HEHIO+ REGIRZ]] |    |    |

| 10 2<br>10 2<br>10 3 |                                       | ADDI | REG [RZ] | # 8             |    |    |

| - 2                  | У                                     | SGTI | REG [P4] | DONE            |    |    |

| <u>د با</u>          | · · · · · · · · · · · · · · · · · · · |      |          |                 |    |    |

|                      |                                       |      |          |                 |    |    |

Indicate in the table below the status of the registers.

(2 points)

| Field F0 F2 F4 F6 R1 R2 R3    Register Status   R2 R3   R3   R2   R3   R3   R4   R4   R4   R4   R4   R4 |       |    |     |    | <u>-</u> | Pegister St | tatus |      |      |     |

|---------------------------------------------------------------------------------------------------------|-------|----|-----|----|----------|-------------|-------|------|------|-----|

|                                                                                                         |       | EO | EO  | F4 |          |             | RI    | R2   | R3   | ••• |

|                                                                                                         | Field | FU | LDI |    | FPU2     |             |       | INTZ | INT3 |     |

Indicate in the table below the state of the store buffers

(1 points)

|         | Store   | Buffers | Store 3 |

|---------|---------|---------|---------|

| ield    | Store 1 | Store 2 | 3,010 3 |

| Di      | FPU 2   |         |         |

| usy     | У       |         |         |

| Address | 0+ [2]  |         |         |

### Section 4. Unrolling (5 points)

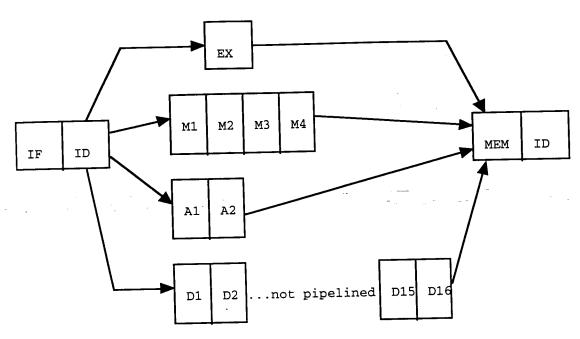

Consider a standard FP pipeline as in the mid-term:

Consider again the loop of the previous question:

• Unroll this loop twice and schedule it for minimal execution time on average when run on the pipeline above Ignore the branch delay and assume that all branches are correctly predicted. (5 points)

# Section 5: Branch predictors (15 points)

Consider this infinite loop and its assembly code translation

```

R1, R0, 1 // init a

ADDI

R2, R0, 1 // init b

ADDI

R1, ELSE

b = 1;

BNEZ

B1:

/* for ever */

while (1) {

R1, R0, 1

ADDI

if (a == 0)

в2

J

a = 1;

R1, R0, 0

ADDI

ELSE:

R1, B3

else

BEZ

B2:

a = 0;

R2, R0, 0

ADDI

if (a != 0)

R2, B1

BNEZ

B3:

R2, R0, 1

b = 0;

ADDI

if (b == 0)

B1

b = 1;

```

In the table below, the successive values of a and b are listed. Notice the period two. The sequence of taken (T) an not taken (N) branch outcomes is also given in the table below.

| · ·          |               |

|--------------|---------------|

|              |               |

| <u>a</u> b   | B1 outcome: T |

| 1 1          | B2 outcome: T |

| 0 1          | B3 outcome: T |

| 0 1          | B1 outcome: N |

| 0 1          | B2 outcome: N |

| 1 1          | B3 outcome: N |

| 1 0          | B1 outcome: T |

| 1 1          | B2 outcome: T |

| 01 And so-on | BZ Odcos.ms.  |

A machine has a 2-bit branch predictor mechanism. What is the performance of this predictor while executin this code in the steady state in terms of correct predictions(s) per iteration? A concise explanation must be TWO BIT PREDICTOR given to get the marks.

```

EACH BRANCH (BI, B2, B3) HAS

BI SEQUENCE: T, N, T, N . --

B2 SEQUENCE: T, N, T, N ---

B3 SEQUENCE: T, N, T, N ---

TWO : 50%

OF

PREPICTION

OUT

CORRECT

ONE

```

A machine has a (1,1) correlating branch predictor. What is its performance while executing the same code the steady state in terms of correct prediction(s) per iteration? Fill the table below to get the marks. (5 points LAST BRANCH NOT TAKENS I LAST BRANCH TAKEN

| LAST BRANCH NOT TAKENS IT LAST | BRANCH TAKEN     |               | UPDATE NO |

|--------------------------------|------------------|---------------|-----------|

| LAST DAMER NOT TANKING         | B1 prediction: N | B1 outcome: T | NO UPDATE |

| B1 prediction bits: NN         | B2 prediction: T | B2 outcome: T |           |

| B2 prediction bits: TT         | B3 prediction: N | B3 outcome: T | UPDATE    |

| B3 prediction bits: NN         |                  | B1 outcome: N | NO UPDAT  |

| B1 prediction bits: TN         | B1 prediction: N | B2 outcome: N | UPPATE N  |

| B2 prediction bits: TT         | B2 prediction: T | B3 outcome: N | NO UPDA   |

| B3 prediction bits: NT         | B3 prediction: N |               | NO UPD    |

| B3 prediction bits. TN         | B1 prediction: T | B1 outcome:   | UPPATE    |

| B1 prediction bits: TN         | B2 prediction: N | B2 outcome: T |           |

| B2 prediction bits: NT         | B3 prediction: T | B3 outcome: T | 190 ca    |

| B3 prediction bits: NT         | B3 prediction:   |               |           |

Average number of correct predictions?

for the code below, supposing that there is a hit in the buffer (that is: predicted taken), but the prediction is incorrect. (5 points)

```

SLTI R5, R1, 0

\\ compare R1 with 0

1.

2.

\\ if R1 >= 0 skip

BNEZ R5, SKIP

SUBI R1, R0, R1

\\ negate

3.

\\ double

4.

SKIP:

MULT R1, R1, R1

5.

\\ store it

SW

R1, 0(R7)

6.

AND

R1, R0, R0

\\ clear R1

```

| SLTI | IF | ID | EX | HE | WB  |    |    |  |   |   |  |  |  |   |

|------|----|----|----|----|-----|----|----|--|---|---|--|--|--|---|

| BNEZ |    | IF | S  | ID | EX  | ME | WB |  |   |   |  |  |  |   |

| NULT |    |    |    | IF | 10* |    |    |  |   |   |  |  |  |   |

| SUBE |    |    | -  |    | ٠.  | IF |    |  | 1 | - |  |  |  |   |

| HULT |    |    |    |    |     |    | IF |  |   |   |  |  |  | - |

KKL RULT '

#### Section 6: Loop level parallelism (15 points)

Consider this loop:

```

for (i = 1; i < 100; ++i) {

/* S1 */

a[i - 1] = c[i - 1] + n;

/* S2 */

b[i] = m + c[i];

a[i] = a[i] + b[i];

/* S3 */

}

```

List all the dependencies: output dependencies, anti-dependencies, and true data dependencies and indicate: each dependency the pair of statements and which are "loop carried" (5 points)

Output Dependencies: SI - \$3

LOOP CARRIED

asi] - a [i-1] SARE

Anti Dependencies:

53 - SI

LOOP CARRIED

Data Dependencies

52-53

Rewrite the loop so it becomes parallel. Solve this problem in two different ways:

• First use software renaming, not changing the structure of the loop: (5 points) asi-i] OF NEXT THAT IS DEPENDENCIES INVOLVE a [1] LOOP CARRIED WRITTEN, NEVER READ . CALL IT TEMPCO] ALWAYS for (---) { TEMP [1-1] = c[1-1]+n b[i] = m + c[i] > a [:] = a [:] + b [:]

Second transform the loop without renaming so it becomes parallel:

(5 points)

SENP PC HIT, F

$$a[o] = c[o] + n$$

$$for(i = 1; i < 99; +ti) {$$

$$b[i] = m + c[i];$$

$$a[i] = a[i] + b[i];$$

$$a[i] = c[i] + n;$$

$$b[i] = m + c[i];$$

$$a[i] = a[i] + b[i];$$

## Section 7: Memory Hierarchy (18 points)

A cache system has B blocks of N words and total storage capacity L (for valid bits, tags, and data) measured in bits. Recall that the degree of associativity A is defined as the number of blocks per set. Assume further that the memory address space is  $2^{Z}$  and that the memory is word addressed (each word has W bits). Call H the hit time, M the miss rate, and P the miss penalty measured in clock cycles.

Consider now this contrived but interesting example (read the whole section before starting). The benchmark test is to visit (read only) all the addresses in the address space exactly once.

• Calculate the AMAT of the cache system for this test as a function of B, N, W, Z, H, and P starting from a blank cache (all the valid bits are off). In developing the formula, take the case of a direct mapped cache, or equivalently A = 1, that is M sets.

AMAT = H + M P  $2^2$  WORDS VISITED

Ly MISS RATE?

NUMBER OF MISSES:  $\frac{2^2}{N}$ RATE =  $\frac{1}{N}$ NUMBER OF ACCESSES:  $2^2$ AMAT = H +  $\frac{P}{N}$  =  $2 + \frac{20}{4} = 7$

LOCALITY DOES NOT APPLY SINCE ALL LOCATIONS VISITED ONCE

• Work out the result for B=16, N=4, A=1, Z=32, W=32, H=2, and P=20. (4 points)

1 MISS, 3 HITS IN CLOCK CYCLES

4 x 2 + 20 FOR EACH BLOCK OF 4 WORD

AVERAGE ACCESS TIME =  $\frac{28}{L}$  = 7 CC.

Note that these last two questions are independent. You can solve the numerical example by reasoning it out and then derive the formula, or you can develop the formula first and then plug the numbers in.

• Bonus question!: Solve the same problems for A = 2 (5 + 5 points

MORE ASSOCIATIVITY DOES NOT CHANGE RESULT.

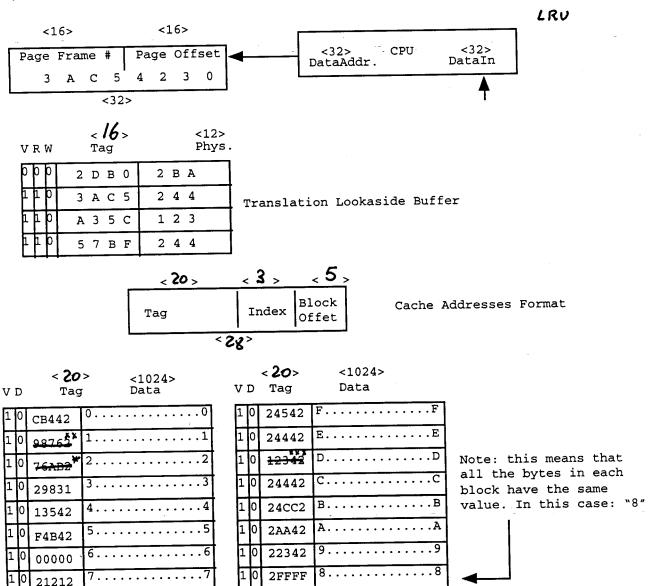

CPU requests this sequence of addresses:3AC54230, A35C2340, and 57BF2344. If there is a miss, ate a replacement by showing which tag gets changed and assume the blocks continue to hold the same In any case, indicate below the values returned to the CPU.

30: PHYS. ADDR. BAC5 244; INDEX : 2 ; TAG: BAC52 ; MISS; RETURN 2-2 OR D. 40: PHYS. ADDR. A35C123; INDEX: 1; TAG: A35C1; MISS; RETURN IN I OR E. E 44: PHYS. ADDR. 578F244; INDEX: 2; TAG: 57BF2; TISS; RETURN D.D OR 2...Z

Set Associative Cache (8 sets of 2 blocks) Write Back, Write Allocate

52

101

F2