| Pipelining                                                                    |    |    |    |     |     |     |     |     |    |

|-------------------------------------------------------------------------------|----|----|----|-----|-----|-----|-----|-----|----|

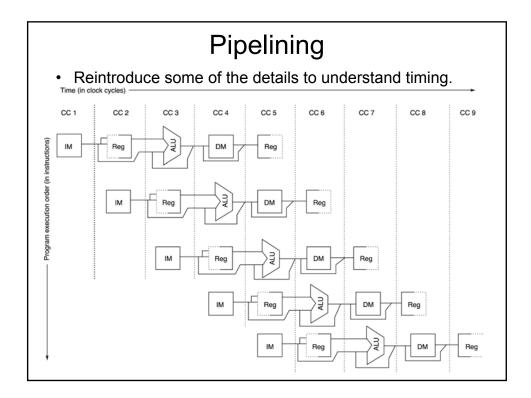

| Classic Five-Stage RISC Pipeline<br>Starts a new instruction each clock cycle |    |    |    |     |     |     |     |     |    |

| Clock number                                                                  |    |    |    |     |     |     |     |     |    |

| Instruction number                                                            | 1  | 2  | 3  | 4   | 5   | 6   | 7   | 8   | 9  |

| Instruction i                                                                 | IF | ID | EX | MEM | WB  |     |     |     |    |

| Instruction i + 1                                                             |    | IF | ID | EX  | MEM | WB  |     |     |    |

| Instruction i + 2                                                             |    |    | IF | ID  | EX  | MEM | WB  |     |    |

| Instruction i + 3                                                             |    |    |    | IF  | ID  | EX  | MEM | WB  |    |

| Instruction i + 4                                                             |    |    |    |     | IF  | ID  | EX  | MEM | WB |

|                                                                               |    |    |    |     |     |     |     |     | 10 |

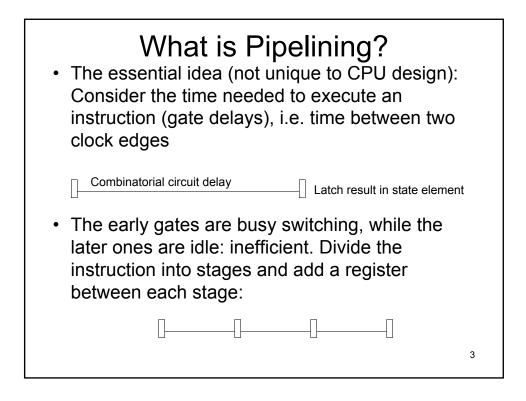

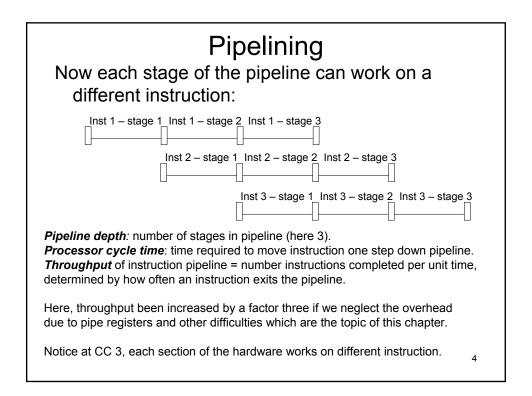

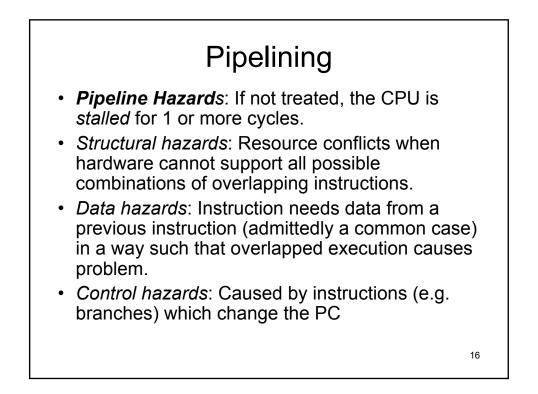

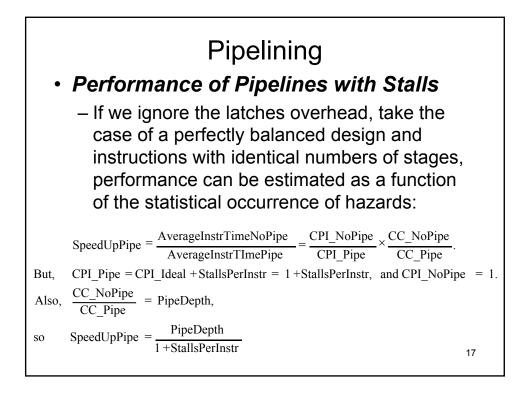

## Pipelining

### Performance optimization

- But there are other issues. We assumed so far that each instruction behaves like a sequence of stages with each stage consuming data produces by the previous stage so they can run in parallel.

- Unfortunately, this is clearly not the case in a program: one instruction can consume in one stage data produced by another instruction in the same or in another stage. There are also cases where two instructions would require the same functional unit simultaneously.

- These problems are collectively called *hazards*. We need some systematic method to reason about these.

| cure is<br>decide<br>this ca<br>causes                        | of co<br>the e<br>se the | ourse<br>extra d<br>e sing | a mo<br>cost is<br>le me | s wort<br>emory | bable<br>h the<br>port l | memo<br>gain i<br>has a | ory su<br>n per<br>huge | ib-sys<br>forma<br>impa      | tem i<br>ince.<br>ict sir | if we<br>In<br>Ice i |

|---------------------------------------------------------------|--------------------------|----------------------------|--------------------------|-----------------|--------------------------|-------------------------|-------------------------|------------------------------|---------------------------|----------------------|

|                                                               |                          |                            |                          | Cloc            | k cycle nu               | mber                    |                         |                              |                           |                      |

| Instruction                                                   | 1                        | 2                          | 3                        | 4               | 5                        | 6                       | 7                       | 8                            | 9                         | 10                   |

| Load instruction                                              | IF                       | ID                         | EX                       | MEM             | WB                       |                         |                         |                              |                           |                      |

| Instruction $i + 1$                                           |                          | IF                         | ID                       | EX              | MEM                      | WB                      |                         |                              |                           |                      |

|                                                               |                          |                            | IF                       | ID              | EX                       | MEM                     | WB                      |                              |                           |                      |

| Instruction $i + 2$                                           |                          |                            |                          | stall           | IF                       | ID                      | EX                      | MEM                          | WB                        |                      |

| $\frac{\text{Instruction } i + 2}{\text{Instruction } i + 3}$ |                          |                            |                          |                 |                          | IF                      | ID                      | EX                           | MEM                       | WB                   |

|                                                               |                          |                            |                          |                 |                          |                         |                         | and the second second second |                           |                      |

| Instruction $i + 3$                                           |                          |                            | -                        |                 |                          |                         | IF                      | ID                           | EX                        | MEM                  |

| <ul> <li>Pipelining</li> <li>Cost of load structural hazard – example:         <ul> <li>Data reference: 40% of mix</li> <li>CPI_ideal of pipelined processor (no structural hazard) = 1</li> <li>Machine 1: processor with no structural hazard</li> <li>Machine 2: processor with structural hazard</li> <li>Machine 2 has clock rate 1.05 x faster than machine 1.</li> </ul> </li> <li>Disregarding any other performance losses, which machine is faster</li> </ul> | r? |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Average instruction time = CPI x ClockCycleTime                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| Machine 1: Average instruction time = ClockCycleTime1                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| Machine 2:<br>Average instruction time =<br>(CPI_ideal + Clocks for hazard) x ClockCycleTime2 =<br>(1 + 0.4 x 1) x ClockCycleTime1/1.05 = 1.3 x ClockCycleTime1                                                                                                                                                                                                                                                                                                         |    |

| Machine 1 is 1.3 x faster!                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |

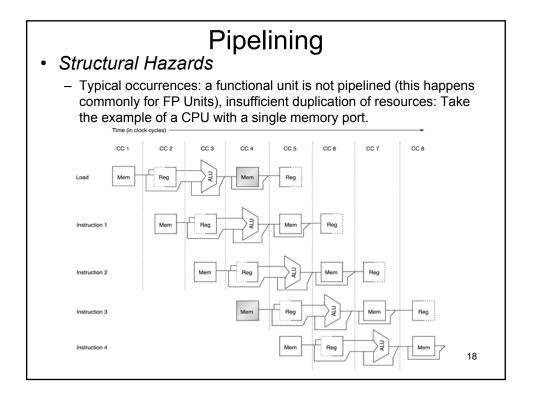

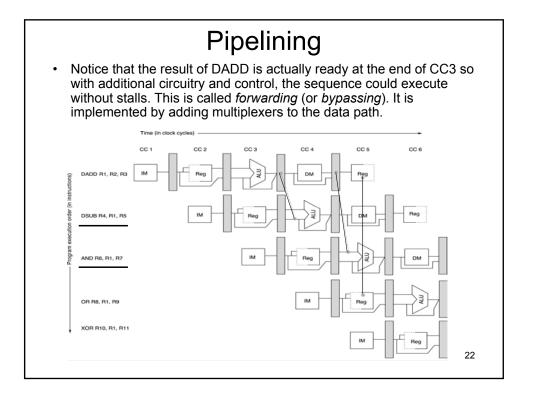

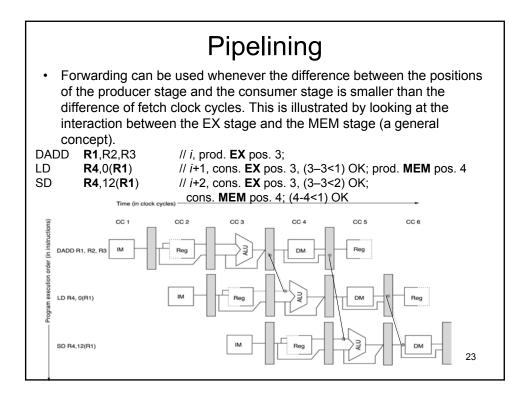

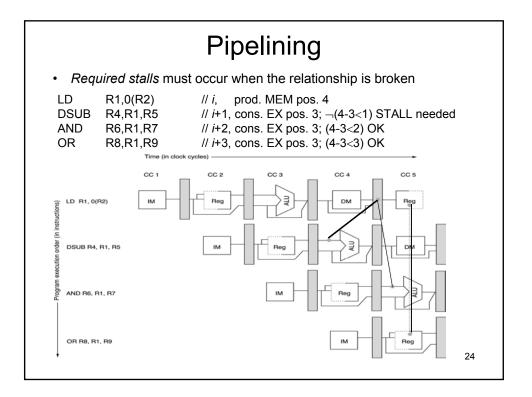

| •    | Again, th | is is mo | re cono | cisely s | een in | the form | n of a t | iming d | liagran | ۱. |

|------|-----------|----------|---------|----------|--------|----------|----------|---------|---------|----|

| LD   | R1,0(R2)  | IF       | ID      | EX       | MEM    | WB       |          |         |         |    |

| DSUB | R4,R1,R5  |          | IF      | ID       | EX     | MEM      | WB       |         |         |    |

| AND  | R6,R1,R7  |          |         | IF       | ID     | EX       | MEM      | WB      |         |    |

| OR   | R8,R1,R9  |          |         |          | IF     | ID       | EX       | MEM     | WB      |    |

| LD   | R1,0(R2)  | IF       | ID      | EX       | MEM    | WB       |          |         |         |    |

| DSUB | R4,R1,R5  |          | IF      | ID       | stall  | EX       | MEM      | WB      |         |    |

| AND  | R6,R1,R7  |          |         | IF       | stall  | ID       | EX       | MEM     | WB      |    |

| OR   | R8,R1,R9  |          |         |          | stall  | IF       | ID       | EX      | MEM     | WB |

| 2 | 5 |  |

|---|---|--|

|   |   |  |

| stalls are<br>pipeline,<br>ordering<br>(one of t | tuations when the CPU either is<br>e required as in the case of load<br>the stalls can be reduced or evindependent instructions This<br>he target-specific back-end cor<br>e consider this: | s not or pa<br>d stalls for<br>ven totally<br>known as | 5 stage MIP<br>eliminated b<br>static schedu | S<br>y re-<br><i>ıling</i> |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------|----------------------------|

|                                                  | a = b + c                                                                                                                                                                                   |                                                        |                                              |                            |

| Damas                                            | d = e - f                                                                                                                                                                                   | O a la a alu                                           |                                              |                            |

|                                                  | mpilation                                                                                                                                                                                   |                                                        | lled code                                    |                            |

| LW                                               | Rb,                                                                                                                                                                                         | LW                                                     | Rb,                                          |                            |

| LW                                               | Rc,                                                                                                                                                                                         | LW                                                     | Rc,                                          |                            |

| Stall                                            |                                                                                                                                                                                             | LW                                                     | Re,                                          |                            |

| DADD                                             | Ra,Rb,Rc                                                                                                                                                                                    | DADD                                                   | Ra,Rb,Rc                                     |                            |

| SW                                               | Ra,                                                                                                                                                                                         | LW                                                     | Rf,                                          |                            |

| LW                                               | Re,                                                                                                                                                                                         | SW                                                     | Ra,                                          |                            |

| LW                                               | Rf,                                                                                                                                                                                         | DSUB                                                   | Rd,Re,Rf                                     |                            |

| Stall<br>DSUB                                    | Pd Po Df                                                                                                                                                                                    | SW                                                     | Rd,                                          |                            |

| SW                                               | Rd,Re,Rf<br>Rd                                                                                                                                                                              |                                                        |                                              |                            |

| 500                                              | Ku,                                                                                                                                                                                         |                                                        |                                              | 26                         |

|                                                  |                                                                                                                                                                                             |                                                        |                                              | 20                         |

|                                                  |                                                                                                                                                                                             |                                                        |                                              |                            |

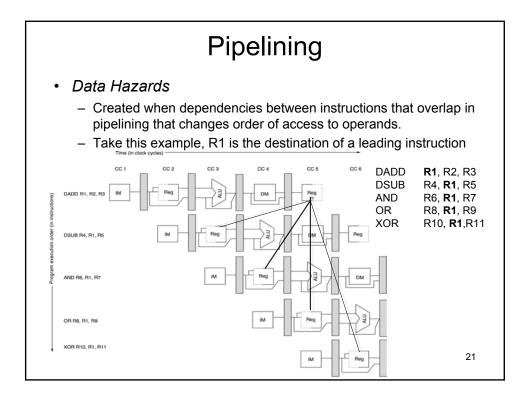

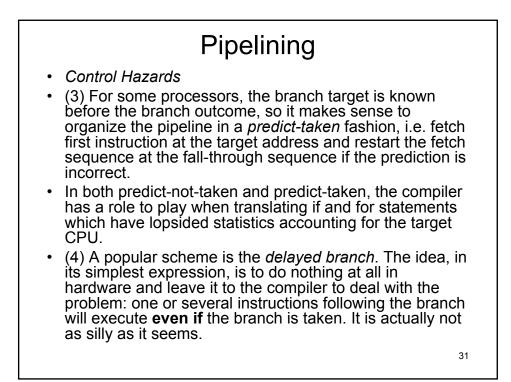

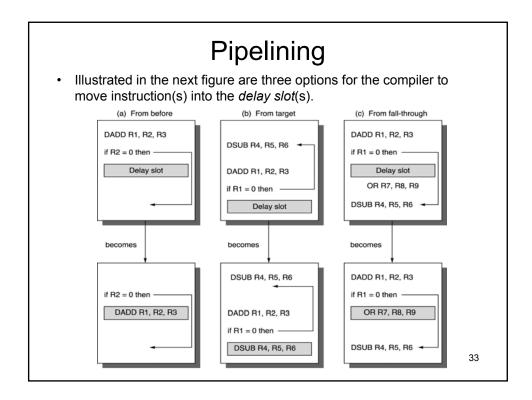

## Pipelining

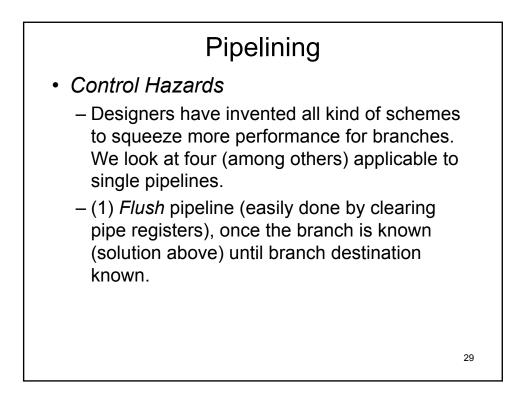

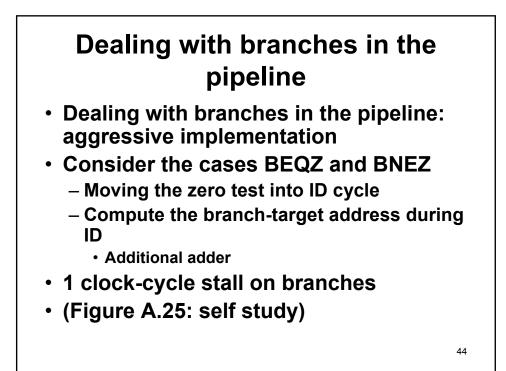

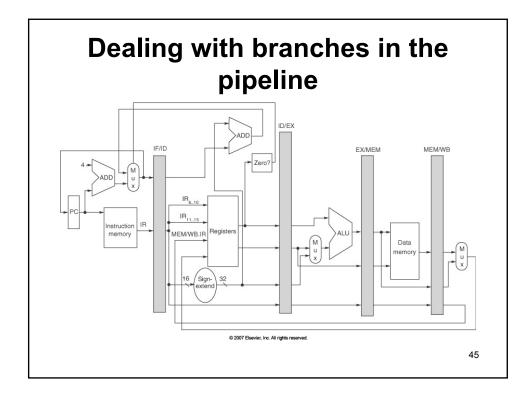

- Control Hazards

- It's the same idea, except now the consuming stage is always IF. The value of the PC is determined later in the pipeline if branch taken. In meantime, if nothing is done in hardware, the CPU will fetch possibly *n* incorrect *fall-through* instructions, where *n* is the position difference between the fetch stage and the stage the branch outcome is determined.

|                                                                                                               |                                           | Pipe                            | elini             | ng                  |                   |                 |     |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------|-------------------|---------------------|-------------------|-----------------|-----|

| <ul> <li>Control Ha<br/>– The simp<br/>is decode<br/>cycle for<br/>instruction<br/>is not tak     </li> </ul> | olest ap<br>ed in II<br>each b<br>on coul | oproach<br>D, resul<br>Dranch y | ting in<br>when i | always<br>n fact th | wastin<br>e fetcł | ig a clo<br>ned | ck  |

| Branch instruction                                                                                            | IF                                        | ID                              | EX                | MEM                 | WB                |                 |     |

| Branch successor                                                                                              |                                           | IF                              | IF                | ID                  | EX                | MEM             | WB  |

| Branch successor + 1                                                                                          |                                           |                                 |                   | IF                  | ID                | EX              | MEM |

| Branch successor $+2$                                                                                         |                                           |                                 |                   |                     | IF                | ID              | EX  |

|                                                                                                              |       | Pi   | peli             | ning                    | 9                            |                         |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|--------------------------------------------------------------------------------------------------------------|-------|------|------------------|-------------------------|------------------------------|-------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Control I                                                                                                    | Haza  | rds  |                  |                         |                              |                         |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| – (2) <i>Pree</i><br>more co<br>fetch in                                                                     | ompli | cate | d. Pro           | oceed                   | d as a                       | above                   | e, bu     | t re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Untaken branch instruction                                                                                   | IF    | ID   | EX               | MEM                     | WB                           |                         |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|                                                                                                              |       |      |                  |                         |                              |                         |           | and the second se |    |

| Instruction $i + 1$                                                                                          |       | IF   | ID               | EX                      | MEM                          | WB                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| Instruction $i + 1$<br>Instruction $i + 2$                                                                   |       | IF   | ID<br>IF         | EX<br>ID                | MEM<br>EX                    | WB<br>MEM               | WB        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|                                                                                                              |       | IF   |                  |                         |                              |                         | WB<br>MEM | WB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| Instruction <i>i</i> + 2                                                                                     |       | IF   |                  | ID                      | EX                           | MEM                     |           | WB<br>MEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | WB |

| Instruction <i>i</i> + 2<br>Instruction <i>i</i> + 3                                                         | IF    | IF   |                  | ID                      | EX<br>ID                     | MEM<br>EX               | MEM       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WB |

| Instruction <i>i</i> + 2<br>Instruction <i>i</i> + 3<br>Instruction <i>i</i> + 4                             | IF    |      | IF               | ID<br>IF                | EX<br>ID<br>IF               | MEM<br>EX               | MEM       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WB |

| Instruction <i>i</i> + 2<br>Instruction <i>i</i> + 3<br>Instruction <i>i</i> + 4<br>Taken branch instruction | IF    | ID   | IF<br>EX         | ID<br>IF<br>MEM         | EX<br>ID<br>IF<br>WB         | MEM<br>EX<br>ID         | MEM       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WB |

| Instruction i + 2<br>Instruction i + 3<br>Instruction i + 4<br>Taken branch instruction<br>Instruction i + 1 | IF    | ID   | IF<br>EX<br>idle | ID<br>IF<br>MEM<br>idle | EX<br>ID<br>IF<br>WB<br>idle | MEM<br>EX<br>ID<br>idle | MEM<br>EX |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WE |

| Pipelining                         |    |    |    |     |     |     |     |     |    |

|------------------------------------|----|----|----|-----|-----|-----|-----|-----|----|

| • Delayed b                        |    |    |    |     |     |     |     |     |    |

| Untaken branch instruction         | IF | ID | EX | MEM | WB  |     |     |     |    |

| Branch delay instruction $(i + 1)$ |    | IF | ID | EX  | MEM | WB  |     |     |    |

| Instruction $i + 2$                |    |    | IF | ID  | EX  | MEM | WB  |     |    |

| Instruction $i + 3$                |    |    |    | IF  | ID  | EX  | MEM | WB  |    |

| Instruction <i>i</i> + 4           |    |    |    |     | IF  | ID  | EX  | MEM | WB |

| Taken branch instruction           | IF | ID | EX | MEM | WB  |     |     |     |    |

| Branch delay instruction $(i + 1)$ |    | IF | ID | EX  | MEM | WB  |     |     |    |

| Branch target                      |    |    | IF | ID  | EX  | MEM | WB  |     |    |

| Branch target + 1                  |    |    |    | IF  | ID  | EX  | MEM | WB  |    |

| Branch target + 1                  |    |    |    |     | IF  | ID  | EX  | MEM | WB |

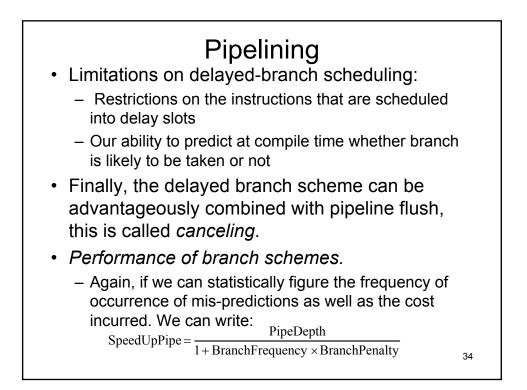

| (assuming no                                                                            | S R4000<br>ne – takes<br>/n + additi<br>stalls on | s 3 pipeline s<br>onal cycle b<br>register in c | stages before k<br>efore branch c<br>onditional com |                                                              |  |

|-----------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------|--|

| <ul> <li>Delay leads to</li> </ul>                                                      | o branch p                                        | penalties for                                   | 3 simplest pre                                      | diction schemes:                                             |  |

| Branch scheme F                                                                         |                                                   |                                                 |                                                     |                                                              |  |

| Flush pipeline                                                                          | 2                                                 |                                                 | 3                                                   | 3                                                            |  |

| Predicted taken                                                                         | 2                                                 |                                                 | 3                                                   | 2                                                            |  |

| Predicted untaken                                                                       | 2                                                 |                                                 | 0                                                   | 3                                                            |  |

| <ul> <li>Find effective a<br/>frequencies:</li> </ul>                                   | addition to C                                     | CPI from bran                                   | ches in pipeline                                    | assuming                                                     |  |

| Uncondition                                                                             | al branch                                         |                                                 | 4%                                                  |                                                              |  |

| Conditional                                                                             | branch, unta                                      | ken                                             | 6%                                                  |                                                              |  |

| Conditional                                                                             | oranch, takei                                     | n                                               | 10%                                                 |                                                              |  |

| Branch scheme un<br>Frequency<br>Flush pipeline<br>Predicted taken<br>Predicted untaken | 4%<br>0.08<br>0.08                                | al untaken<br>6%<br>0.18<br>0.18<br>0           | taken<br>10%<br>0.3<br>0.2<br>0.3                   | All branches<br>20%<br>0.56<br>0.46<br>0.38<br><sub>35</sub> |  |

|                                                                                         |                                                   |                                                 |                                                     |                                                              |  |

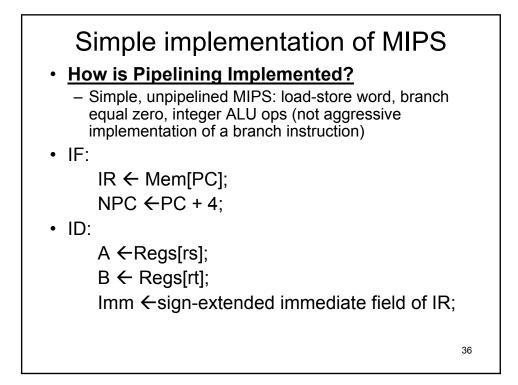

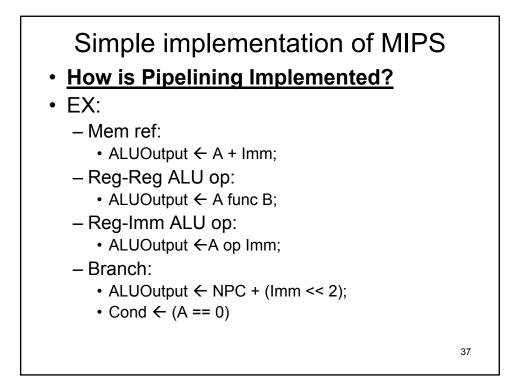

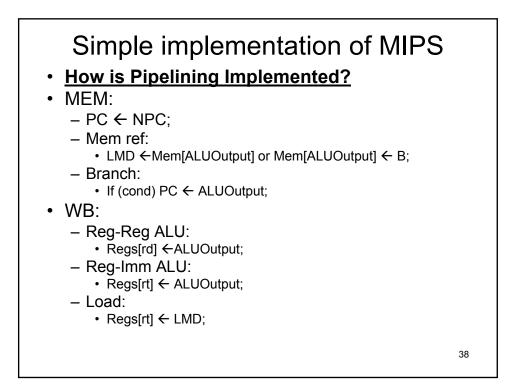

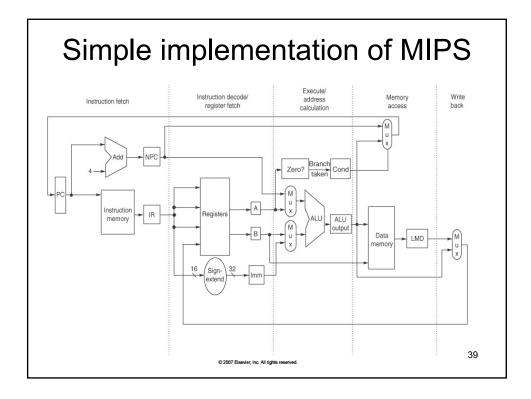

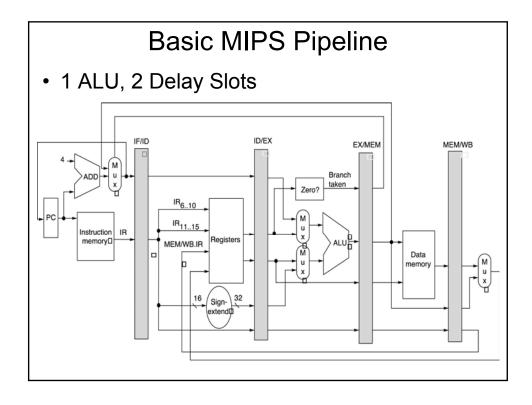

|       | Basic MIPS pipeline                                                                                                   |                                                                                                           |                                                                                         |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|

| Stage | Any instruction                                                                                                       |                                                                                                           |                                                                                         |  |  |  |  |  |

| IF    | IF/ID.IR←Mem[PC];<br>IF/ID.NPC,PC ←(if ((EX/MEM.opcode=<br>{PC+4});                                                   | ==branch) & EX/MEM.cond) {EX.MI                                                                           | EM.ALUOutput} else                                                                      |  |  |  |  |  |

| ID    | ID.EX.A ←Regs[IF/ID.IR[rs]]; ID/EX.B<br>ID/EX.NPC ←IF/ID.NPC; ID/EX.IR ←II<br>ID/EX.Imm ← sign-extend(IF/ID.IR[imm    | F/ID.IR;                                                                                                  |                                                                                         |  |  |  |  |  |

|       | ALU instruction                                                                                                       | Load or store instruction                                                                                 | Branch instruction                                                                      |  |  |  |  |  |

| EX    | EX/MEM.IR ←ID/EX.IR;<br>EX/MEM.ALUOutput ← ID.EX.A func<br>ID/EX.B; or<br>EX/MEM.ALUOutput ← ID/EX.A op<br>ID/EX.Imm; | EX/MEM.IR to ID/EX.IR<br>EX/MEM.ALUOutput ← ID/EX.A<br>+ ID/EX.Imm;<br>EX/MEM.B ←ID/EX.B;                 | EX/MEM.ALUOutput<br>← ID/EX.NPC +<br>(ID/EX.Imm<<2);<br>EX/MEM.cond ←<br>(ID/EX.A ==0); |  |  |  |  |  |

| MEM   | MEM/WB.IR ←EX/MEM.IR;<br>MEM/WB.ALUOutput<br>←EX/MEM.ALUOutput;                                                       | MEM/WB.IR ←EX/MEM.IR;<br>MEM/WB.LMD ←<br>Mem[EX/MEM.ALUOutput]; or<br>Mem[EX/MEM.ALUOutput]<br>←EX/MEM.B; |                                                                                         |  |  |  |  |  |

| WB    | Regs[MEM/WB.IR[rd]]<br>←MEM/WB.ALUOutput; or<br>Regs[MEM/WB.IR[rt]]<br>←MEM/WB.ALUOutput;                             | For load only;<br>Regs[MEM/WB.IR[rt]]<br>←MEM/WB.LMD;                                                     | 41                                                                                      |  |  |  |  |  |

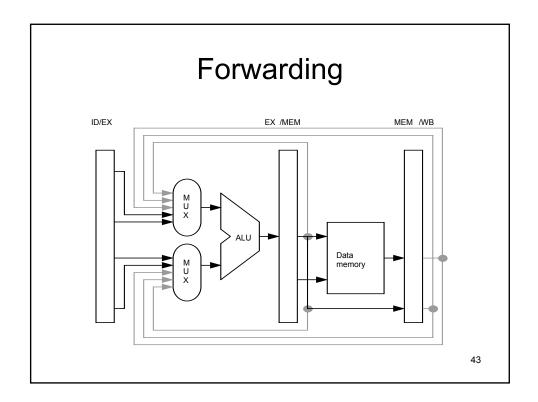

# Implementing Control for the MIPS pipeline

- All data hazards can be checked during ID phase. If exists – stalled before *issued* (ID – EX). Can determine what forwarding will be needed during ID and set controls then.

- · Detect interlocks early!

- Pipeline hazard detection hardware compare destination and sources of adjacent instructions (only need to compare on 2 instructions following instruction that wrote destination)

- Once hazard detected, insert pipeline stall (change instruction to no-op)

- Forwarding from: ALU output, data memory output to

ALU input, data memory input, zero detection

- This implies additional multiplexer inputs + add connections from pipeline registers

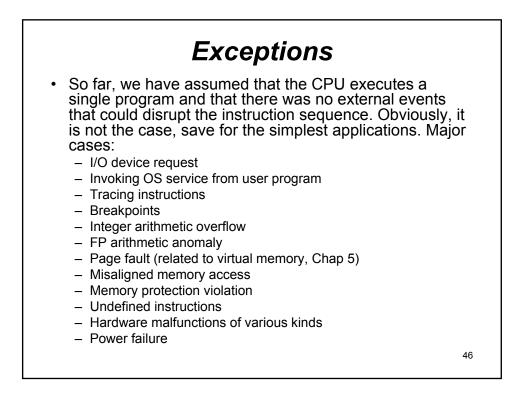

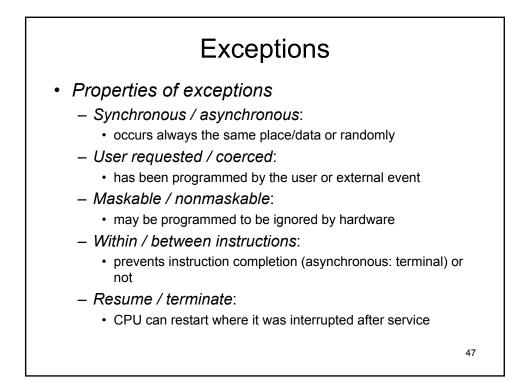

|                    |          | Exce      | eptions     |         |           |

|--------------------|----------|-----------|-------------|---------|-----------|

|                    | <b>A</b> |           |             | Detwoor |           |

| I/O                | Async.   | Coerced   | Nonmaskable | Between | Resume    |

| OS Invoke          | Sync.    | Requested | Nonmaskable | Between | Resume    |

| Trace Instr. ex.   | Sync.    | Requested | Maskable    | Between | Resume    |

| Breakpoint         | Sync.    | Coerced   | Maskable    | Between | Resume    |

| Int. Overflow      | Sync.    | Coerced   | Maskable    | Within  | Resume    |

| FP Exception       | Sync.    | Coerced   | Maskable    | Within  | Resume    |

| Page Fault         | Sync.    | Coerced   | Nonmaskable | Within  | Resume    |

| Misalig. Acc.      | Sync.    | Coerced   | Maskable    | Within  | Resume    |

| Mem. Protection    | Sync.    | Coerced   | Nonmaskable | Within  | Resume    |

| Undef. Instruction | Sync.    | Coerced   | Nonmaskable | Within  | Terminate |

| Hardw. Fault       | Async.   | Coerced   | Nonmaskable | Within  | Terminate |

| Power Failure      | Async.   | Coerced   | Nonmaskable | Within  | Terminate |

|                                                                                                                            | E                                                                                 | ксер                                                              | tions                                                   | s in N                                         | ЛР                                            | S                                                 |                                                  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------|-----------------------------------------------|---------------------------------------------------|--------------------------------------------------|--|--|--|--|

| <ul> <li>Some</li> </ul>                                                                                                   | of the                                                                            | excep                                                             | otions t                                                | hat ca                                         | in ha                                         | ppen:                                             |                                                  |  |  |  |  |

| IF                                                                                                                         | Page Fault, misalignment, memory protection                                       |                                                                   |                                                         |                                                |                                               |                                                   |                                                  |  |  |  |  |

| ID                                                                                                                         | Undefined instruction                                                             |                                                                   |                                                         |                                                |                                               |                                                   |                                                  |  |  |  |  |

| EX                                                                                                                         | Arithmetic exception                                                              |                                                                   |                                                         |                                                |                                               |                                                   |                                                  |  |  |  |  |

| MEM                                                                                                                        | Page Fault, misalignment, memory protection                                       |                                                                   |                                                         |                                                |                                               |                                                   |                                                  |  |  |  |  |

| WB                                                                                                                         | None                                                                              |                                                                   |                                                         |                                                |                                               |                                                   |                                                  |  |  |  |  |

| Example<br>LD IF<br>DADD                                                                                                   | ID<br>IF                                                                          | EX<br>ID                                                          | MEM<br>EX                                               | WB<br>MEM                                      | WB                                            |                                                   |                                                  |  |  |  |  |

| Multiple exce<br>arithmetic exc<br>LD and an ins<br>Exceptions ra<br><b>Solution:</b> Po<br>the pipe whic<br>they can be p | ception. The<br>struction particular<br>ised by LE<br>st all except<br>is checker | ere can a<br>age fault i<br>) must be<br>otions in a<br>ed when t | Ilso be a d<br>n the IF of<br>serviced f<br>a status ve | ata page<br>the DAD<br>first and the ctor asso | fault in t<br>D which<br>nen thos<br>ciated w | the MEM s<br>occurs ease of the D<br>vith each in | stage of the<br>arlier.<br>ADD.<br>nstruction in |  |  |  |  |

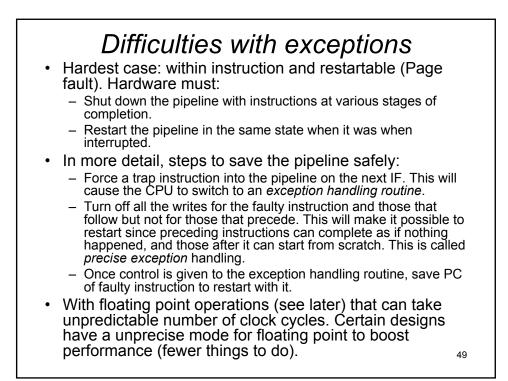

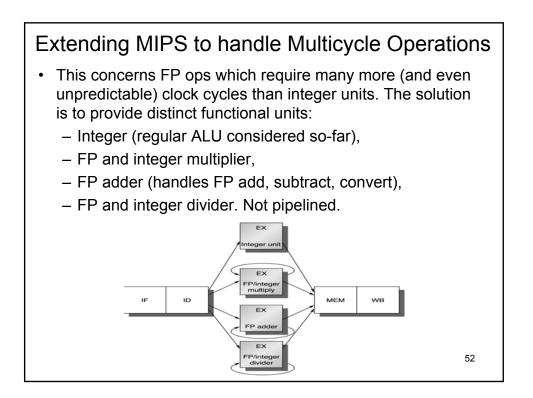

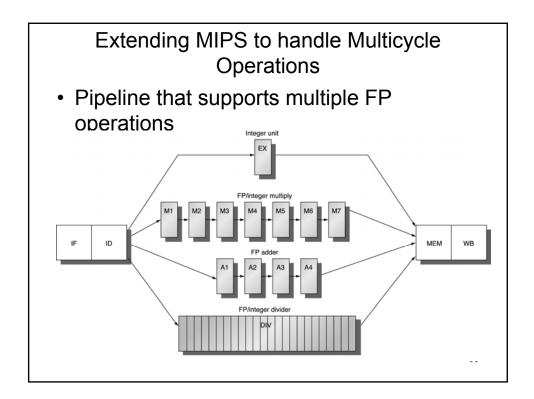

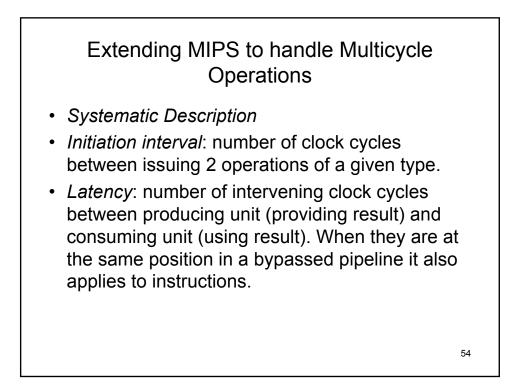

### Extending MIPS to handle Multicycle Operations

| Functional Unit              | Latency | Initiation Interval |  |  |  |

|------------------------------|---------|---------------------|--|--|--|

| Integer ALU (EX)             | 0       | 1                   |  |  |  |

| Data Memory (integer and FP) | 1       | 1                   |  |  |  |

| FP add                       | 3       | 1                   |  |  |  |

| FP and int. multiply         | 6       | 1                   |  |  |  |

| FP and int. divide           | 23      | 24                  |  |  |  |

Comments:

•Possibility for structural hazards, *e.g.* divide unit not pipelined, several instructions could compete to write to register.

•New kinds of hazards: an instruction fetched after another instruction could write the register before the earliest one! •More and longer stalls.

55

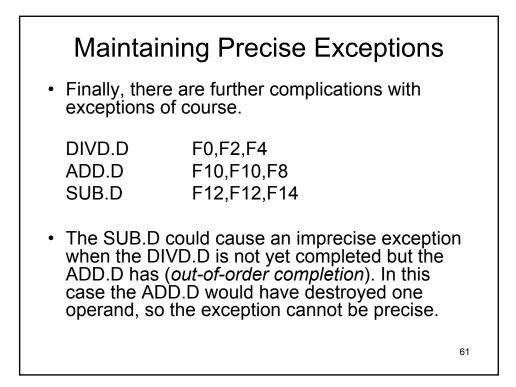

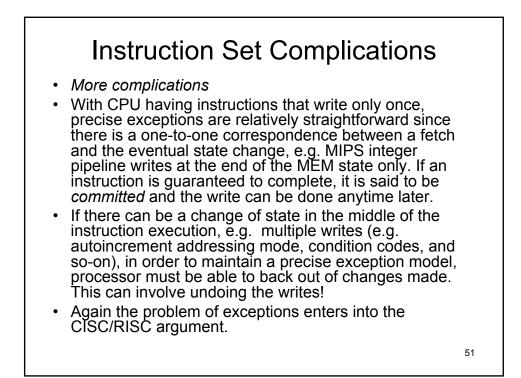

#### Classification of data hazards We need a way to reason more systematically about data hazards. In the next chapter we will generalize this even further. For now, consider pairs of instructions which *depend* on each other because they share a register written by a producer and read by a consumer instruction. This holds for bypassed data paths since forwarding can only reduce latency but not make it negative! With this in mind, look at all cases: RAW (read after write). A pair of instructions has a consumer trying to read before the producer writes. The most common type: e.g. a = 0; ...; a = 1; b = a + 1, then, we expect b to have the value 2, not 1. WAW (write after write). A pair of instructions are producers but the instruction that writes first appears after in the program: - e.g. a = 1+2; ...;a = 2\*3, then, we expect a to have the value 6, not 3. WAR (write after read). A producing instruction occurs after a consuming instruction but writes before the consumer reads: - e.g. a = 1; b = a + 1; a = 2, then, we expect b to have the value 2, not 3.

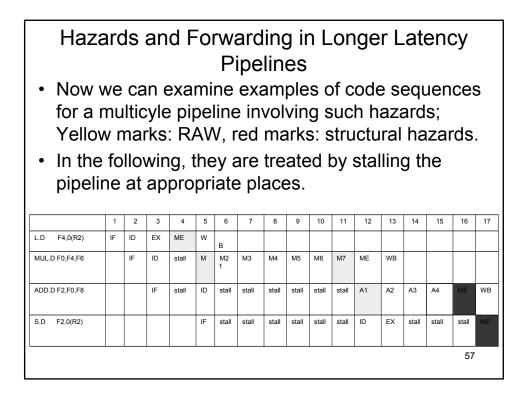

| Haza                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rds | s a  | nd    | F    |        |      | din<br>elir | -     |      | on   | ger    | La    | ate  | nc   | y  |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------|--------|------|-------------|-------|------|------|--------|-------|------|------|----|----|

| <ul> <li>In this exacuses the provident of the second second</li></ul> | men | nory | / but | at 1 | 11, tł | nree | instr       | uctio | ns c | ompe | ete fo | or th | e re | gist | er |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1   | 2    | 3     | 4    | 5      | 6    | 7           | 8     | 9    | 10   | 11     | 12    | 13   | 14   | 15 | 16 |

| MUL.D F0,F4,F6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IF  | ID   | M1    | M2   | M3     | M4   | M5          | M6    | M7   | ME   | WB     |       |      |      |    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | IF   | ID    | EX   | ME     | WB   |             |       |      |      |        |       |      |      |    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |      | IF    | ID   | EX     | ME   | WB          |       |      |      |        |       |      |      |    |    |

| ADD.D F2,F4,F6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |      |       | IF   | ID     | A1   | A2          | A3    | A4   | ME   | WB     |       |      |      |    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |      |       |      | IF     | ID   | EX          | ME    | WB   |      |        |       |      |      |    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |      |       |      |        | IF   | ID          | EX    | ME   | WB   |        |       |      |      |    |    |

| L.D F2,0(r2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      |       |      |        |      | IF          | ID    | EX   | ME   | WB     |       |      |      | 58 |    |

Hazards and Forwarding in Longer Latency Pipelines

There is a number of structural hazards. The way they are treated is dependent on the details of hardware design. For example, most machines would not allow two instructions in the same stage to share the same pipe register.

Hazards and Forwarding in Longer Latency Pipelines

- In summary, multicycle operation introduce new kinds of hazards which need to be detected and treated. In general, three checks must be performed before an instruction can *issue*, that is transit from decode to execute. Assuming that all hazard detection is done in the ID stage:

- Check for structural hazards, delay until the required unit is available (e.g. divide unit here).

- Check for RAW hazard. Delay until the source registers are not listed as pending destinations.

- Check for WAW hazard. Delay the instruction ID.