## Review of Basic Computer Architecture

ECSE 425 Winter 2007

#### Instruction Set Architecture (ISA)

- Computers run programs made of simple operations called "instructions"

- The list of instructions offered by the machine is the "instruction set"

- The instruction set is what is visible to the programmer (really the compiler, although humans can directly program in "assembly language").

## Instructions

- Two kinds of information in a computer:

- instructions

- data

- Instructions are stored as numbers, just like data

- Instructions and data are stored in the memory

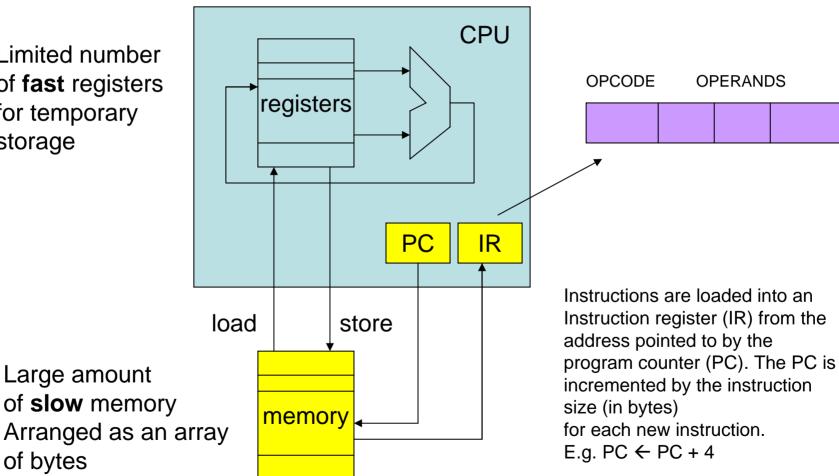

# **Basic Computer Organization**

Limited number of fast registers for temporary storage

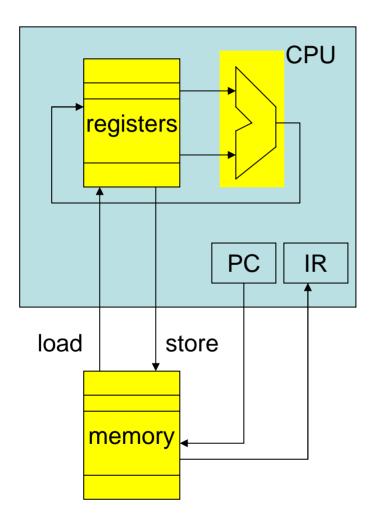

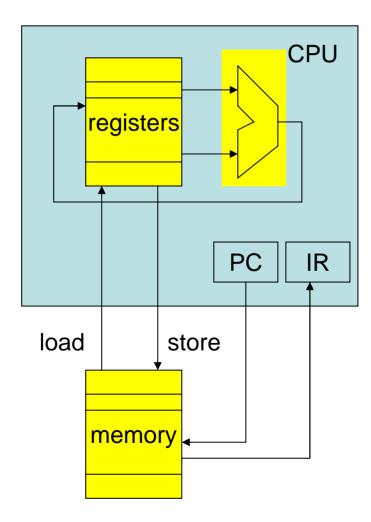

## Load/Store Architecture (Reg-Reg)

- Instructions can **ONLY** get their data and store their data from/to registers.

- The register numbers are specified in the operand fields of the instruction

- Since data is stored in memory, we need special "load" and "store" instructions for transfers between registers and memory. These two instructions are the ONLY ones allowed to access memory

#### Load/Store Architecture (Reg-Reg)

• **RISC** architectures are load/store. The regularity of this architecture enables fast organizations using pipelining (Appendix A).

• **CISC** machines (e.g. Intel IA-32) permit instructions to get their data from both registers and memory (mem-reg). These highly irregular architectures (memreg, variable-length instructions) are practically impossible to pipeline.

• The advantage of them is that they produce shorter programs (no loads or stores needed, variable-length instr.d), but memory today is cheap and compilers can't really use complex instructions anyways.

• Modern "CISC" machines really just translate the CISC instructions to a set of RISC instructions and run those.

• done purely for compatability reasons.

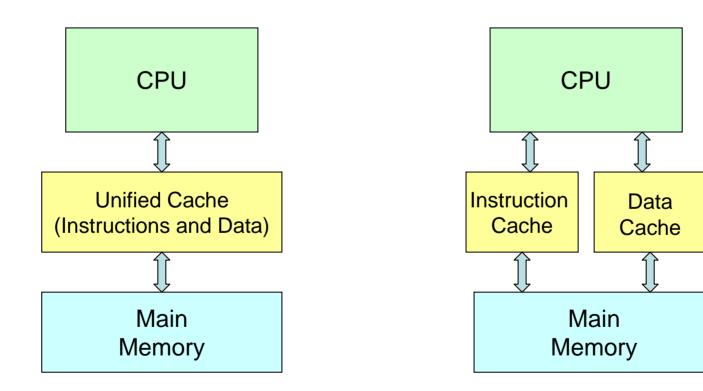

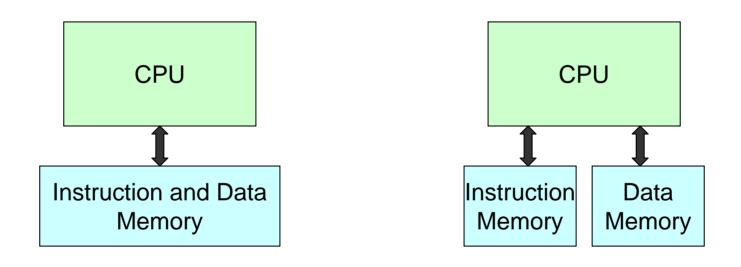

#### Harvard vs. Von Neumann Architectures

Von-Neumann

Harvard

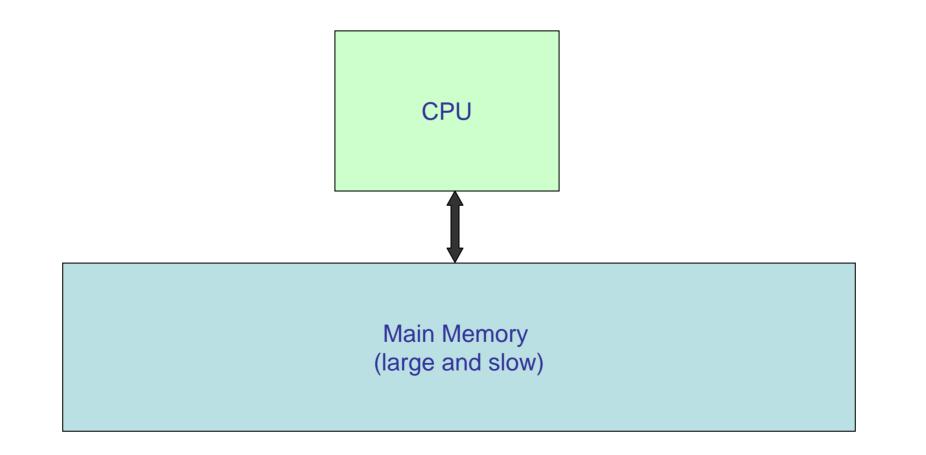

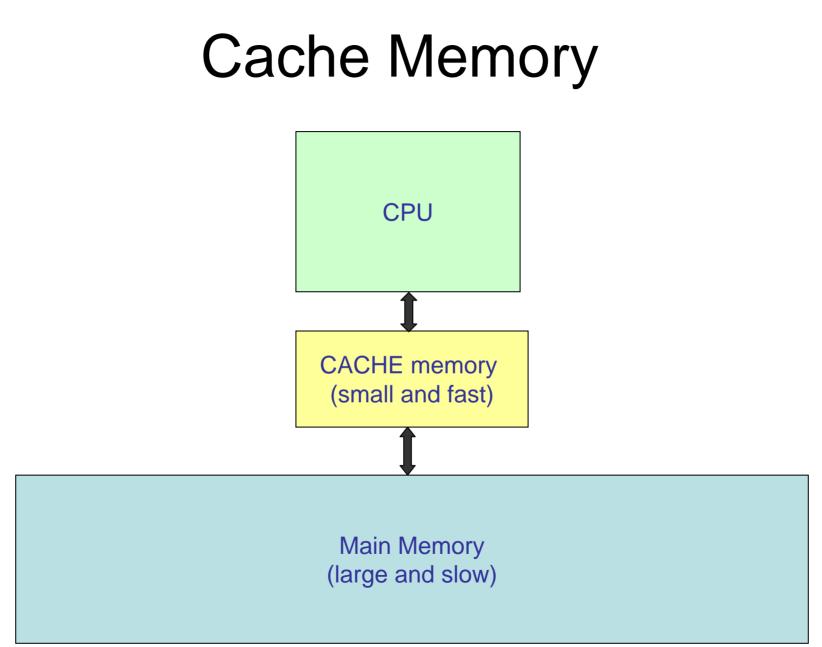

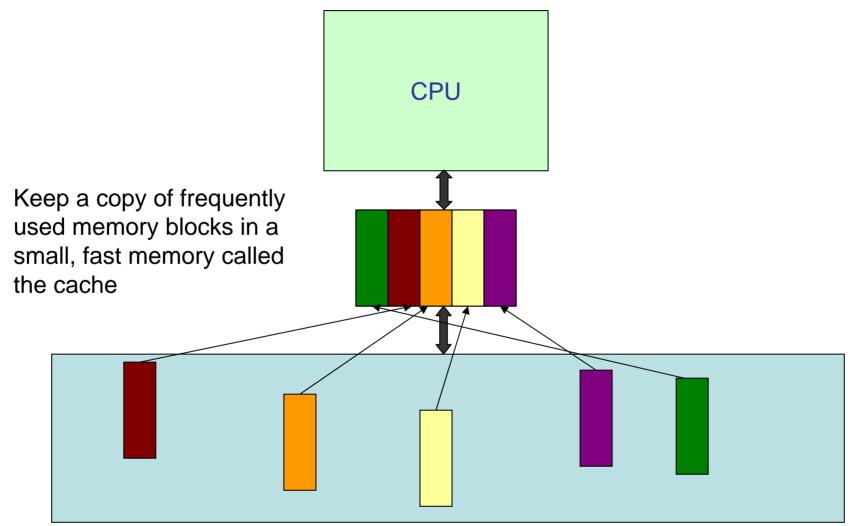

## **Cache Memory**

## **Cache Memory**

#### **Cache Architectures**