# ECSE-323 Digital System Design

VHDL Lecture #4

**begin** -- begin architecture block

```

counter1 : process(reset,Clk)

```

#### begin

if reset = `1' then

count <= 0;

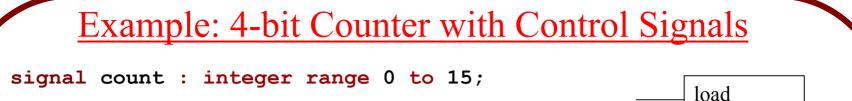

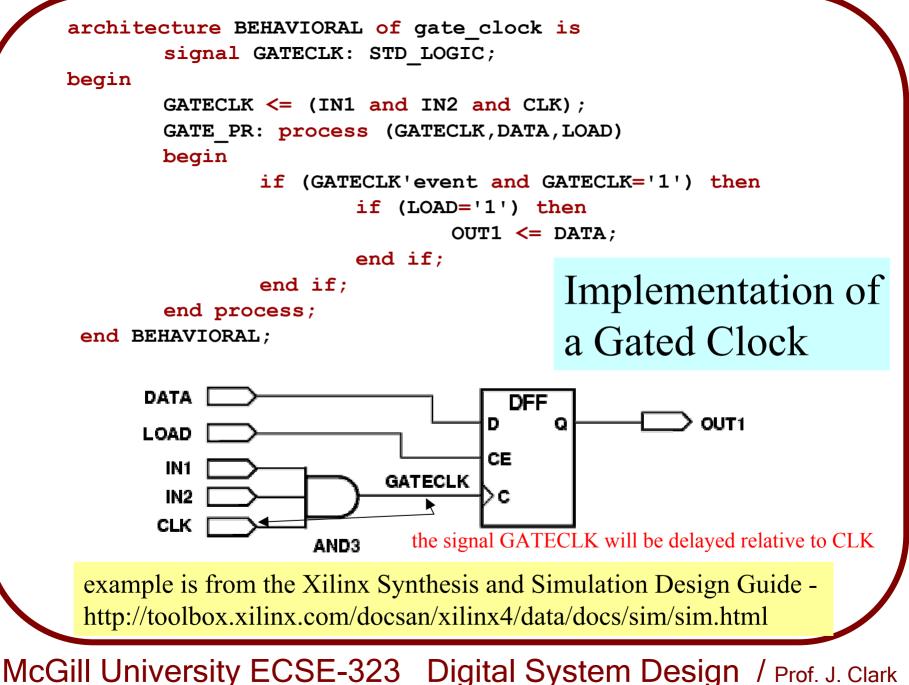

- elsif Clk = '1' and Clk'event then

- if enable = `1' then

reset

enable

ldata

Clk

up/down

count

```

elsif updown = `1' then count <= count + 1;</pre>

```

if load = 1' then count <= ldata;

```

else count <= count - 1;</pre>

```

```

end if; -- if load

```

```

end if; -- if enable

```

end if; -- if reset

end process;

### How to Enable a Clocked Operation:

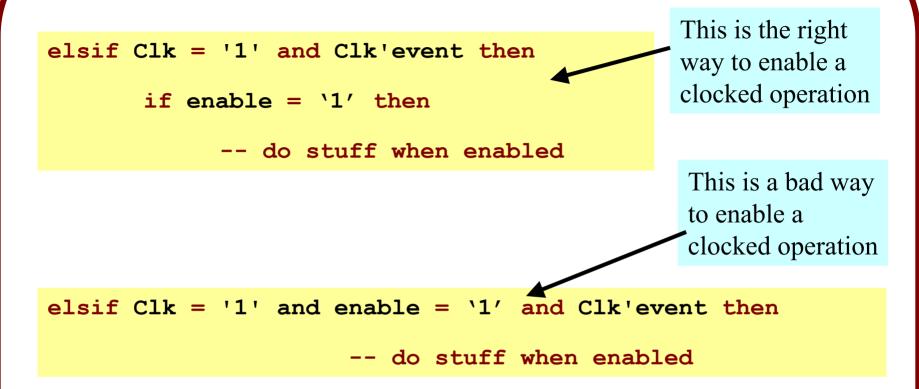

Why is this type of VHDL construct bad? It may confuse the compiler. It may create a *gated clock* (causing clock skew and glitches and slowing down the system)

# **Arithmetic Signal Types and Operations**

**std\_logic\_vector(N downto 0)** defines an (N+1)-bit unsigned binary number whose LSB is bit 0 and MSB is bit N.

#### S<=X+Y;

This expression describes an (N+1)-bit adder without carry in or carry out. The signal **S** has N+1 bits (and not N+2).

# Note:

# VHDL requires that at least one of the operands on the RHS have the same bit length as the LHS.

To add in a Carry input and output we can write:

#### S2 <= ('0' & X) + Y + Cin;

where S2 has one more bit than X and Y

**&** is the VHDL *concatenation* operator

It combines two vectors into a single longer vector.

for example:

signal X, Y : std\_logic\_vector(1 downto 0);

signal Z : std\_logic\_vector(3 downto 0);

X <= "11"; Y <= "10"; Z <= X & Y; -- Z = "1110"

# **Question**: How can we represent *signed* numbers in VHDL?

# **Answer**: define a new signal type, along with associated arithmetic operators

# Signed vs. Unsigned Signal Types

**USE ieee.std\_logic\_unsigned.all** interprets all *std\_logic\_vector* signals as unsigned binary numbers.

**USE ieee.std\_logic\_signed.all** interprets all *std\_logic\_vector* signals as signed binary numbers (2's complement).

If you want to mix *both* signed and unsigned signals then include

# **USE** ieee.std\_logic\_arith.all

You *must* then explicitly say what types are intended:

signal X : SIGNED;

signal X : UNSIGNED;

The use ieee.std\_logic\_arith.all statement should be included *after* the **use ieee.std\_logic\_1164.all** statement.

# **Integer Signal Type**

The *integer* signal type is very useful for implementing counters.

signal X : INTEGER range -16 to 15;

If the range is left out, the default range is used:

$$-(2^{31}-1)$$

to  $(2^{31}-1)$

The number of bits in an integer signal is not specified explicitly. The compiler determines how many bits to allocate to the signal.

The integer data type is built in to the VHDL standard, hence *no library needs to be included* to use this type.

signal X : integer range -32768 to 32767;

In the above example, 16 bits would be allocated to the signal **X**.

There are *conversion functions* to convert between the various signal types.

These conversions are often necessary because in VHDL the types of *signals* on either side of an assignment statement must be the *same*.

#### **Commonly used conversion routines are:**

```

CONV_INTEGER(operand);

CONV_UNSIGNED(operand);

CONV_SIGNED(operand);

CONV_STD_LOGIC_VECTOR(operand, size);

```

**operand** can be of type *integer*, *unsigned*, *signed*, or *std\_logic*.

Example

signal Y : integer range 0 to 100; signal X : std\_logic\_vector(6 downto 0); X <= CONV\_STD\_LOGIC\_VECTOR(Y,7); Y <= CONV\_INTEGER(X);</pre>

### OK, let's look at some examples

```

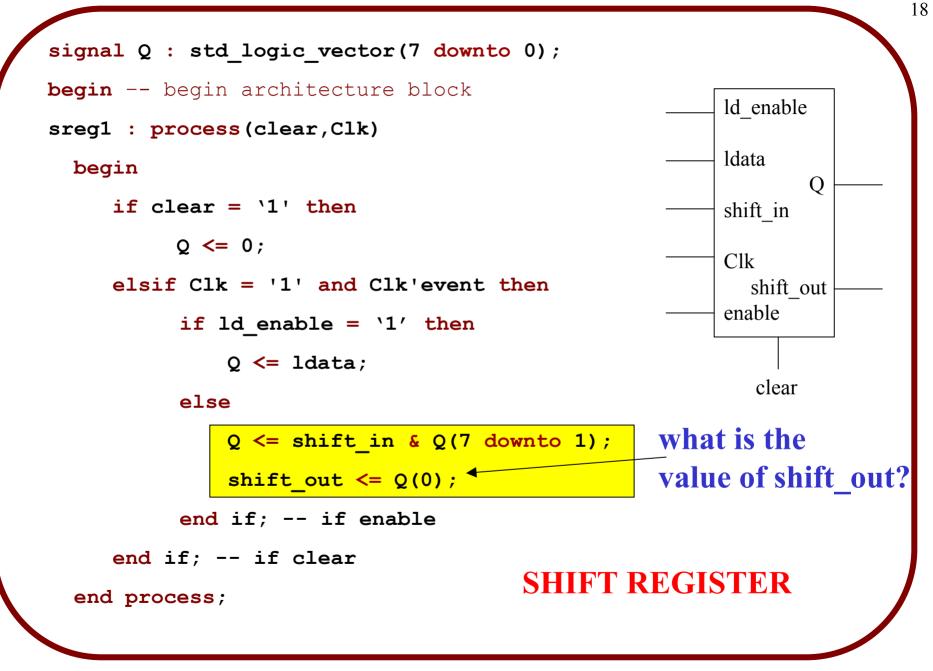

Q <= shift_in & Q(7 downto 1);</pre>

```

shift\_out <= Q(0);</pre>

Suppose that Q = "11010110" going into the process block, and that shift\_in = '0'.

After evaluation of the process block we have that Q = "01101011"

shift\_out will be assigned the value of Q(0)

before the process block is evaluated, i.e.

shift out = 0, not shift out = 1

This is because events on signals created as a result of assignments within a process block actually don't take effect (or aren't *scheduled*) *until the end of the process block is reached*.

The values of *all signals* inside of a process block are the values they have at the beginning of the process block.

```

This circuit

signal count : integer range 0 to 639;

provides a pulse

signal pulse : std logic;

that is one clock

begin -- begin architecture block

period wide every

div1 : process(clear,Clk)

begin

640 clock pulses.

pulse <= '0'; -- give a default value</pre>

if clear = '1' then

count <= 639;

elsif Clk = '1' and Clk'event then

if count enable = '1' then

if count = 0 then

pulse <= '1'; count <= 639;</pre>

else count <= count - 1; -- count down</pre>

end if; -- if count

end if; -- if count enable

end if; -- if clear

FREQUENCY DIVIDER

end process;

```

21

Why do we count down instead of counting up?

Because it often takes *less circuitry* to detect when count = 0 than to detect when count = 639.

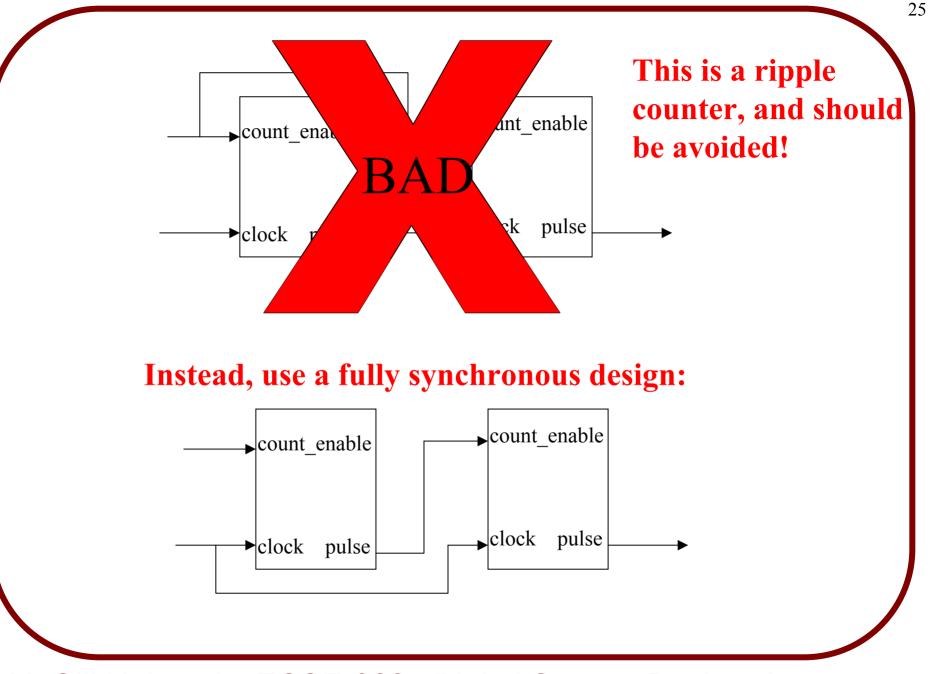

A common use for frequency divider circuits is to effectively slow down clocking of a circuit.

# But, you should not use the pulse signal as a clock!

Instead, use it as a control signal, such as a counter enable.

For example, suppose we want to make a circuit that generates a *pulse* once every *640 clock pulses* and another one every *640\*640 clock pulses*.

# We can do this by having one frequency divider circuit drive another.

# Why are ripple counters bad?

# Because they are slow. Outputs do not all change at the same time.

# Why are they slow?

- 1. Because the clock input to a circuit element is delayed relative to the clock input of the preceding element. Thus any feedback to the preceding element (such as in an FSM) will be delayed, requiring a reduction in clock frequency.

- 2. Ripple clock signals must be routed through logic cells (slow) rather than via dedicated (fast) clock wiring.

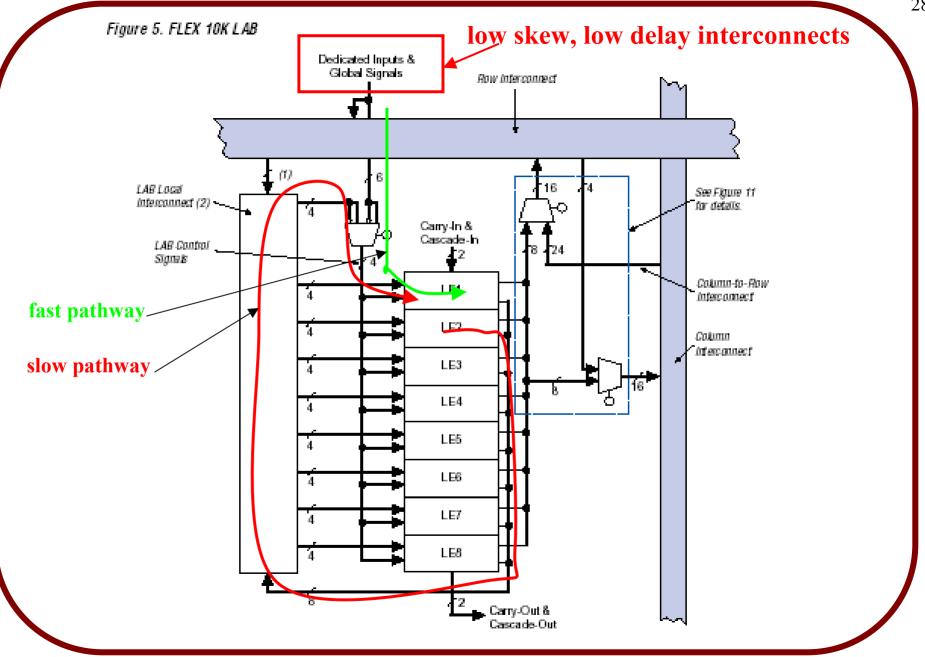

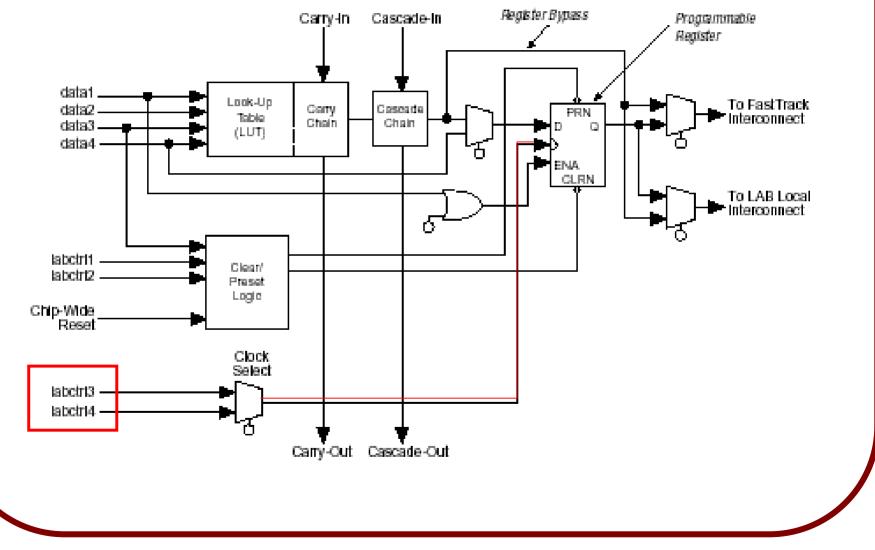

#### Figure 6. FLEX 10K Logic Element

A complex counter example.

Suppose we want to count in the following sequence: *{0, 1, 4, 5, 8, 9, 12, 13, 0,...}*

A keen observer will note that this sequence can be obtained by adding *1* if the count is even, and adding *3* if the count is odd.

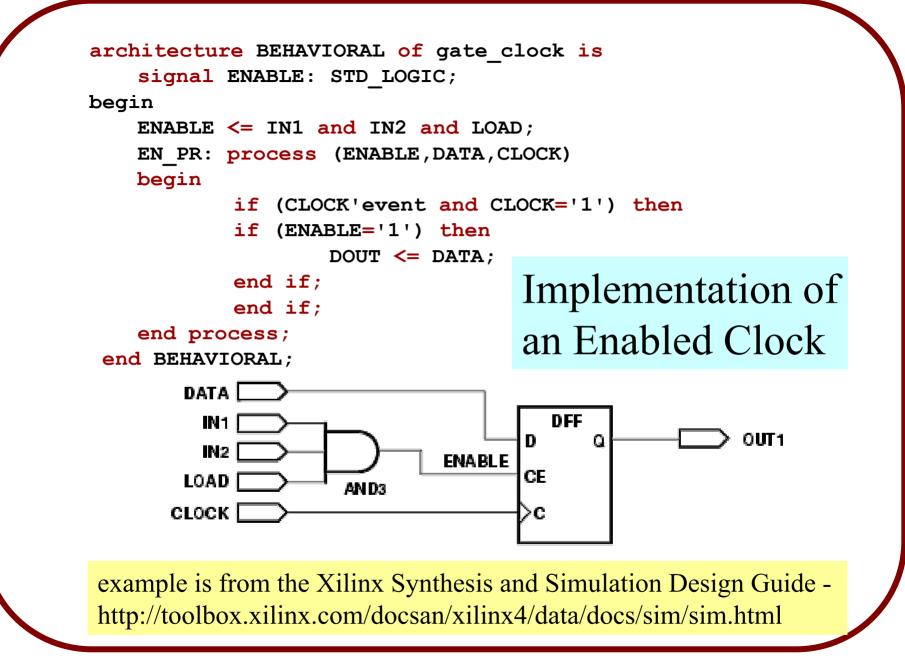

signal count : integer range 0 to 15;

```

signal odd : std_logic;

```

**begin** -- begin architecture block

```

count1 : process(clear,Clk)

```

#### begin

if clear = `1' then

count <= 0; odd <= '0';</pre>

elsif Clk = '1' and Clk'event then

```

if count enable = '1' then

```

```

odd <= not odd;</pre>

```

if odd = '0' then count <= count + 1;</pre>

else count <= count + 3;</pre>

end if; -- if odd

```

end if; -- if count enable

```

```

end if; -- if clear

```

```

end process;

```

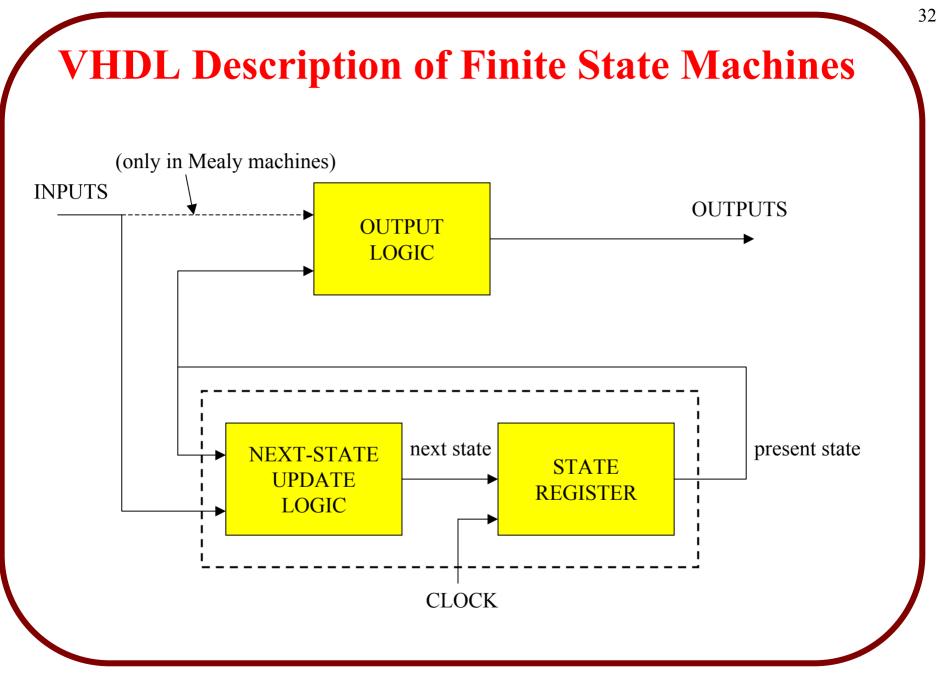

FSMs should be described using 2 process blocks

- one for the state update (and state storage)

- one for the output logic

For some *Moore machines* it might be more readable to combine these *two* process blocks into a *single* process block.

#### **Define a "state" signal type to hold the state**

**TYPE** State\_type **IS** (list of signal values);

The name for the new signal type

The list of *values* that the new signal type can have. These can be numerical values, or symbolic state names, for example.

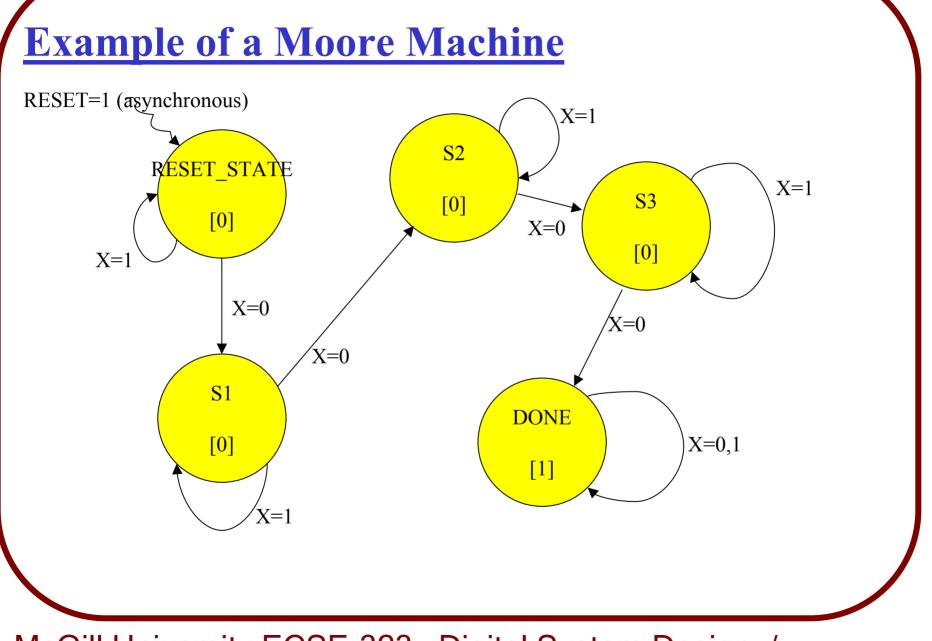

### **Example**

```

architecture behavioural of FSM is

TYPE state_signal IS

(RESET_STATE, S1, S2, S3, DONE);

SIGNAL state : state_signal;

begin

```

You must place the signal TYPE declaration in the declarations area of the architecture.

# *Case statements* are very useful for describing *finite state machines*.

### **Description using 2 process blocks**

```

architecture behavioural of FSM is

TYPE state signal IS (RESET STATE, S1, S2, S3, DONE);

SIGNAL state : state signal;

begin

state update : process (clk,reset)

begin

if reset = '1' then

state <= RESET STATE;</pre>

elsif clk'EVENT and clk='1' then

case state is

when RESET STATE =>

if x = '0' then state <= S1; end if;

when S1 =>

if x = '0' then state <= S2; end if;

when S2 =>

if x = '0' then state <= S3; end if;

```

```

when S3 =>

if x = '0' then state <= DONE; end if;</pre>

when DONE =>

state <= DONE;</pre>

end case;

end if; -- if reset

end process;

output logic : process(state)

begin

case state is

when RESET STATE => Z \leq '0';

when S1 => Z <= '0';

when S2 \implies Z \iff 0';

when S3 => Z <= '0';

when DONE \Rightarrow Z <= '1';

end case;

end process;

Note: all cases are accounted for,

end behavioural;

so we do not need a when others

McGill University ECSE-323 Digital System Design / Prof. J. Clark

```

39

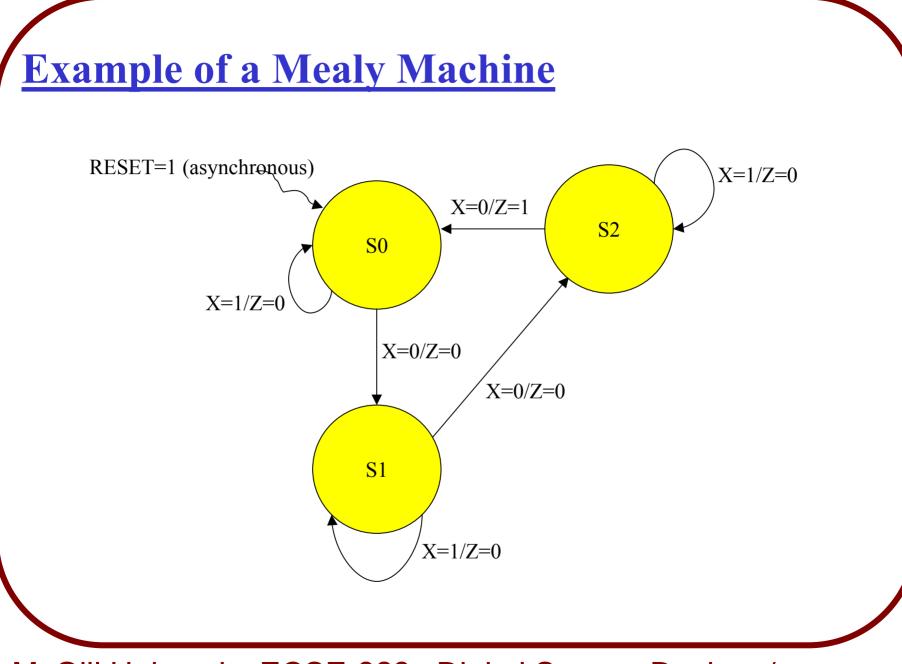

# **VHDL Description of a Mealy Machine**

```

architecture behavioural of FSM is

TYPE state signal IS (S0, S1, S2);

SIGNAL state : state signal;

begin

state update : process (clk,reset)

begin

if reset = '1' then

state <= RESET STATE;</pre>

elsif clk'EVENT and clk='1' then

case state is

when S0 =>

if x = '0' then state <= S1; end if;</pre>

when S1 =>

if x = '0' then state <= S2; end if;

when S2 =>

if x = '0' then state <= S0; end if;

end case;

end if; -- if reset

end process;

```

VHDL Description of a Mealy Machine (cont.)

```

output_logic : process (state, X)

begin

case state is

when S0 => Z <= '0';

when S1 => Z <= '0';

when S2 => Z <= not X;

end case;

end process;

end behavioural;</pre>

```

Note that the sensitivity list contains both the signals state and X

# **State Assignment Methods**

The Quartus compiler assigns the state bits for each state, based on some state optimization procedure.

The very first state in the list in your state signal type declaration will be assigned the state bit values of *all zeroes*.

This is useful for *power-on reset* where upon powering on of an FPGA all flipflops get set to zero, and will therefore go to the first state in the list.

# Therefore, make the first state in the state type list be the *RESET* state! (or some initial state)

# **State Assignment Methods**

If you don't like the state assignment that Quartus gives you, or you want to use your own assignment (to implement *one-hot state encoding*, for example) you can tell the Quartus program what to use.

This is done by specifying a user-defined *ATTRIBUTE*

architecture behaviour of fsm is

type state\_type is (S0, S2, S3);

attribute ENUM\_ENCODING : STRING;

attribute ENUM\_ENCODING of state\_type :

TYPE IS "00 01 11";

signal states : state\_type;