#### Department of Electrical Engineering Introduction to Computer Engineering 1 Assignment 6: Computer Architecture

This assignment is not to be handed in, but is intended as a tutorial to help you understand the key elements of Chapter 5. All figure and page numbers are from Patterson and Hennessy, 3rd edition (with numbers from the 2nd edition given in parentheses afterwards).

### Question 1:

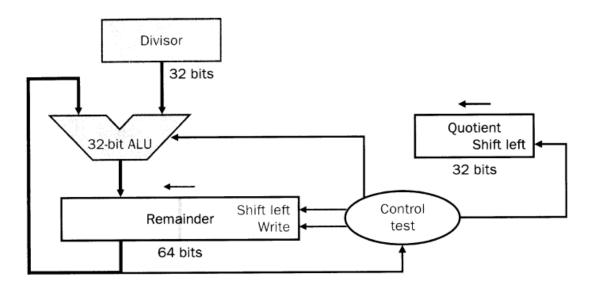

Consider the following datapath:

Like the more complex control unit of the MIPS cpu, e.g. Figure 5.40, p 345 (Fig 5.50, p. 416, 2nd ed.), the control can be implemented as a finite state machine. To make the problem more interesting, assume that a non-restoring algorithm is used for division. What changes are required in the datapath? Next, draw the finite state machine diagram for the modified datapath (assume numbers are positive).

### Question 2

(5.8) Suppose there were a MIPS instruction, called bcp, that copied a block of words from one address to another. Assume that this instruction requires that the starting address of the source block is in register \$1 and the destination address is in \$2, and the number of words to copy is in \$3 (which is > 0). Furthermore, assume that the values of these registers as well as register \$4 can be destroyed in executing this instruction (so that the registers can be used as temporaries to execute the instruction).

Write the MIPS assembly language program to implement block copy. How many instructions will be executed to perform a 100-word block copy? Using the CPI of the instructions in the multicycle implementation, how many cycles are needed for the 100-word block copy?

## Question 3

(5.9) Microcode has been used to add more powerful instructions to an instruction set; let's explore the potential benefits of this approach. Give a microprogram to implement the bcp instruction. To implement this instruction, we will need to extend the microinstruction format. In the extended format we allow the SRCI and SRC2 fields to contain either an explicit register designator, and the SRC2 field to contain a small constant (five bits in length). We also allow the ALU destination field to contain an explicit register specifier. Finally, we will need to have microinstructions that can conditionally branch, since implementing bcp will require a loop. Assume the sequencing field is extended to allow a branch based on the 0 bit out of the ALU. The label specifies another microinstruction.

How many microinstructions will be executed to copy a block of 100 words? How does this compare to the number of MIPS instructions required? Assuming each microinstruction takes one cycle, how does the cycle count of the microcode implementation compare to the implementation using MIPS instructions in the previous question? How do you explain the difference?

#### **Question 4**

(5.10) To implement the bcp instruction in Question 3, we needed to expand the microinstruction. Assume that each field of the microinstruction is encoded separately and that there will be at most 1024 microinstructions. Find the width of each field in the original and extended microinstruction and the total widths. Remember to include bits that describe fields that can have different types of values (e.g., SRC1 in the extended microinstruction).

## **Question 5:**

(5.11) We wish to add the instruction addiu (Add Immediate Unsigned) to the singlecycle datapath described in Chapter 5. This instruction is described in Chapter 3. Add any necessary datapaths and control signals to the single clock datapath of Figure 5.17 on page 307 (Fig. 5.19, p 360, 2nd ed.). You can photocopy the existing datapath to make it faster to show the additions.

## **Question 6:**

(5.12) Show the additions to the table in Figure 5.18 on page 308 (Fig 5.20, p. 361, 2nd ed.) needed to set the control lines that were added in Question 2 for the instruction addiu.

### **Question 7:**

(5.13) We wish to add the datapath parts and control needed to implement the addiu instruction in the multiclock datapath and control. Show the additions to the datapath and control lines of Figure 5.28 on page 323 (Fig. 5.33, p. 383, 2nd ed.) needed to implement this instruction in the multicycle datapath.

### Question 8

(5.14) Show the steps in executing the addiu instruction in the multiclock datapath, using the same breakdown of steps as used in pages 325 through 329 (385 through 388, 2nd. ed.).

#### Question 9

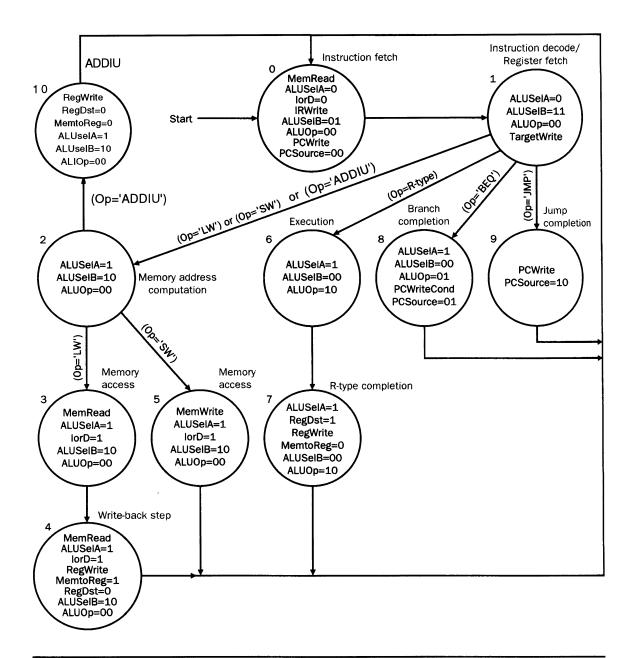

(5.15) Show the additions to the finite state machine of Figure 5.38 on page 339 (5.42, p. 396, 2nd ed.) needed to implement the addiu instruction.

Question #1

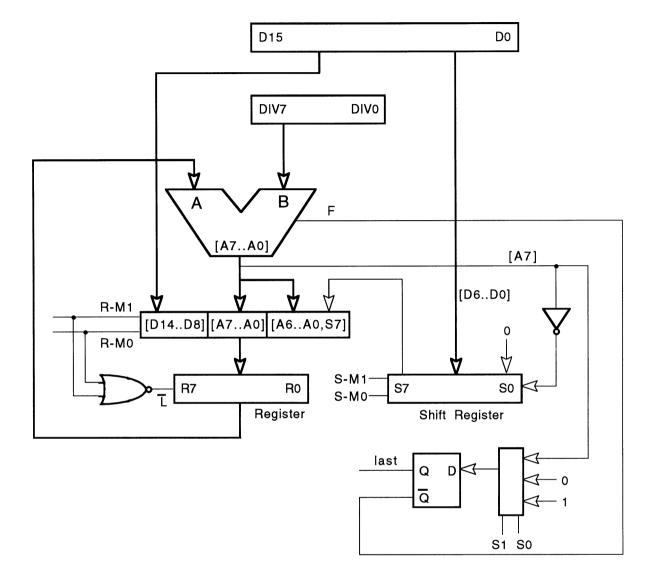

- The nodified detapath is shown on the next page (3) for an 8-bit ALU. To work in MIPS all we have to do is enlarge widths by 4x.

- · Modifications

- The Ahu can add or subtract. A 1-bit register is added to record the operation performed on the previous iteration.

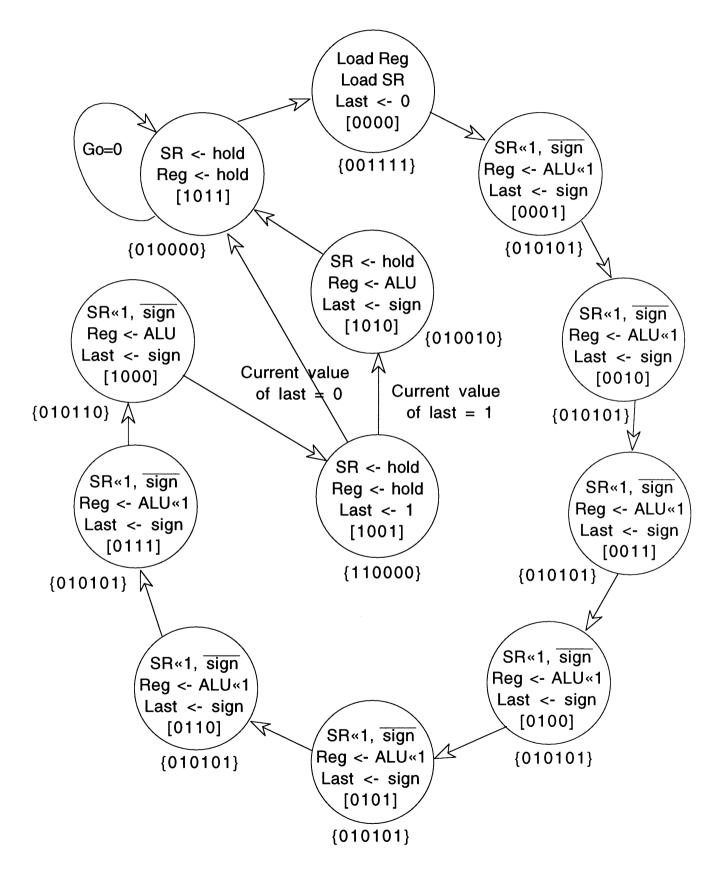

- State Diagram

Is shown on page 4. The bits in curly brackets

nidicate the data path settings for that state,

e.g., { 010 10 (} => { SL=0, S0=1, S-M=0, S-M0=1,

R-MI=0, R-MI= (}

Pay special attention to states 8,9, and (0)

State 8 loads the register without shifting.

If the result from 8 is negative, one additional

uddition will have to be partor ned. During this

step, the quotient is held constant (shift register does not shift). We don't know the result we get to Stake 9.

State 9 is where the decision on the final restore is made. Both registers are held constant, and the multiplexer controlling the D flip-flop is set Question # 1: cout.

2

so that D=1 on the next state transition. The decision on whether to do the add (State 10) or skip the add is made on the basis of the current value of the flip-flop. If lest = 1, a negative result was obtained, so we go to State 10. Otherwise we go to 11.

State 11 is just an idle state that freezes the registers so we can observe the result. It stags in 11 until the external imput " 50" changes from 0 to 1.

In all, Il states are needed. I added an extrastate (and an additional input) to give the circuit a "display" feature.

# Non-Restoring Divider: 8-bit Datapath

**Datapath Operations**

| <b>R-M1</b> | R-M0       | Function             |

|-------------|------------|----------------------|

| 0           | 0          | [R7R0] < [R7R0]      |

| 0           | 1          | [R7R0] < [A6A0],[S7] |

| 1           | 0          | [R7R0] < [A7A0]      |

| 1           | 1          | [R7R0] < [D14D7]     |

| <b>S</b> 1  | <b>S</b> 0 | Function             |

| 0           | 0          | D < 0                |

| 0           | 1          | D < A7               |

| 1           | 0          | N/A                  |

| 1           | 1          | D < 1                |

#### S-M1 S-M0 Function

- [S7..S0] <-- [S7..S0] 0 0 0

- [\$7..\$0] <-- [\$6..\$0],[A7] 1

- 0 [S7..S0] <-- [0],[S7..S1]

- [S7..S0] <-- [DIV6..DIV0],[0] 1 1

- F Function

1

- [A7..A0] <-- A + B 0 1

- [A7..A0] <-- A B

State Diagram for Non-Restoring Divider

Legend: {S1 S0 S-M1 S-M0 R-M1 R-M0}

4

1/

. 304:-221B April 97

Assignment 6

P \* H p 358, 5.9

| LABEL  | ALY                                                                | SRCI                                                                                                                       | SRCZ                                                                       | Ah4<br>destinction | Memory | Mensig<br>register  | PCUnile<br>control | Sequencing                                      |

|--------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------|--------|---------------------|--------------------|-------------------------------------------------|

| 6cp 10 | A29<br>A29<br>A29<br>A29<br>A29<br>A29<br>A29<br>A29<br>A29<br>A29 | \$ <br>\$ <br>\$2<br>\$2<br>\$2<br>\$3<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$ | Extend<br>Extend<br>Extend<br>Extend<br>Extend<br>-1<br>-1<br>\$ 0<br>\$ 0 | 2                  |        | Write rt<br>Read rt |                    | seq<br>seq<br>seq<br>seq<br>seq<br>fetch<br>bcp |

· Microcode is entered via fetch and dispatch table.

Microprogram is executed as an INSTRUCTION, hence there is no "it", no., return is via "fetch" secucice.

Total cycles: B cycles per iteration × 100 = 200 cycles

+ 2 cycles for the fetch = 202 cycles.

N.B. The instruction specifies what register rt is.

Comparing: 802/1603 => Microcode saves 2 cycles / iteration as no instruction have to be fetched and decoded. The difference corresponds to 4 instructioner 2 cycles / iteration.

Assignment 6

3/

| 364-22103<br>April 97  |          | Assignment 6 |

|------------------------|----------|--------------|

| Pett p 359, 5.10 cont. | Original | Extended     |

| ALU control:           | 2        | 2            |

| SRC1:                  | l        | 7            |

| SRC 2 :                | 2        | Ê            |

| ALU dest.:             | 1        | 7            |

| Memory:                |          | 2            |

| Menory register:       | ス        | 2            |

| PCWrite control:       | 2        | 2            |

| Seanencing :           | <u></u>  | 13           |

|                        | 14       | 43           |

4/

5/

Pall p 359, 5.16

| LABEL ALUCHI. SRCI SRC2 ALUdost Memory Reg Write Sequencing |            |                        |                  |          |        |            |             |              |

|-------------------------------------------------------------|------------|------------------------|------------------|----------|--------|------------|-------------|--------------|

| LABEL                                                       | ALY CH.    | SRCI                   | SRC2             | ALU dost | MEMORY | Men<br>Req | PC<br>Urite | Sequencing   |

| Addity                                                      | 999<br>499 | <b>FS</b><br><b>(S</b> | extend<br>extend | ۲t       |        |            |             | seç<br>fetch |

|                                                             | 1          |                        |                  |          |        |            |             | - · · ·      |

୍ଦ

**FIGURE 5.47 The complete finite state machine control for the datapath shown in Figure 5.39.** The labels on the arcs are conditions that are tested to determine which state is the next state; when the next state is unconditional, no label is given. The labels inside the nodes indicate the output signals asserted during that state; we always specify the setting of a multiplexor control signal if the correct operation requires it. Hence, in some states a multiplexor control will be set to 0. In Appendix C, we will examine how to turn this finite state machine into logic equations and look at how to implement those logic equations.